# THESIS REPORT

Ph.D.

**An Architectural Framework for VLSI Time-Recursive Computation with Applications**

by E. Frantzeskakis Advisor: J. Baras

Ph.D. 93-6

Sponsored by the National Science Foundation Engineering Research Center Program, the University of Maryland, Harvard University, and Industry

#### ABSTRACT

Title of Dissertation: An Architectural Framework

for VLSI Time-Recursive Computation

with Applications

Emmanuel Frantzeskakis, Doctor of Philosophy, 1993

Dissertation directed by: Professor John Baras

Department of Electrical Engineering

The time-recursive computation model has been proven as a particularly useful tool in audio, video, radar and sonar real-time data processing architectures. Unlike the FFT based architectures, the time-recursive ones require only local communication, they imply linear implementation cost and they operate in a single-input multiple-output (SIMO) manner. This is appropriate for the above applications since the data are supplied serially. Also, the time-recursive architectures are modular and regular and they allow high degree of parallelism; thus they are very appropriate for VLSI implementation.

In this dissertation, we establish an architectural framework for parallel time-recursive computation. We consider a class of linear operators (or signal transformers) that are characterized by discrete time, time invariant, compactly supported, but otherwise arbitrary kernel functions. We specify the properties of linear operators that can be implemented efficiently in a time-recursive way. Based on these properties, we develop a systematic routine that produces a time-recursive architectural implementation for a given operator. We demonstrate the use and effectiveness of this routine by means of specific examples, namely the Discrete Cosine Transform (DCT), the Discrete Fourier Transform (DFT) and the Discrete Wavelet Transform (DWT).

By using this architectural framework we obtain novel architectures for the uniform-DFT QMF bank, the cosine modulated QMF bank, the 1-D and 2-D Modulated Lapped Transform (MLT), as well as an Extended Lapped Transform (ELT). Furthermore, the architectural implementation of the Cepstral Transform and a Short Time Fourier Transform are considered based on the time-recursive architecture of the DFT. All of the above designs are modular, regular, with local communication and linear cost in operator counts. In particular, the 1-D MLT requires 2N + 3 multipliers, 3N + 3 adders and N - 1 rotation circuits, where N denotes the data block size. The 2-D MLT requires N + 1 multipliers, N + 1 adders and N + 1 rotation circuits and no matrix transposition. The ELT has basis length equal to N + 1 multipliers, N + 1 adders and N + 1 rotation circuits. These results are expected to have a significant impact on real-time audio and video data compression, in frequency domain adaptive filtering and in spectrum analysis.

# An Architectural Framework for VLSI Time-Recursive Computation with Applications

by

Emmanuel Frantzeskakis

Dissertation submitted to the Faculty of The Graduate School of The University of Maryland in partial fulfillment of the requirements for the degree of Doctor of Philosophy

1993

# Advisory Committee:

Professor John Baras, Chairman/ Advisor

Assistant Professor K.J. Ray Liu

Professor Joseph Jájá

Associate Professor Steven Tretter

Associate Professor Nariman Farvardin

Associate Professor Ahmet Oruc

# **DEDICATION**

To my wife Ioanna, my son Nicholas and my parents Nicholas and Vassiliki.

# ACKNOWLEDGMENTS

I would like to express my gratitude to my thesis advisor Dr. John Baras for providing an abundance of opportunity to explore diverse areas of research and for his encouragement, guidance and inspiration throughout the course of my graduate studies. Especially, I appreciate the academic freedom I was given. I am indebted to Dr. Ray Liu who gave me the opportunity and inspiration to broaden my interests and research in many ways and served as a constant source of encouragement. I thank the other members of my advisory committee Dr. J.Jájá, Dr. N.Farvardin, Dr. S.Tretter and Dr. A.Oruc for the unforgetable experience I have had collaborating with them.

A number of fellow students also merit special acknowledgment for serving as sounding boards for ideas, offering suggestions, comments and support over the years. I thank Bernie Frankpitt, Yan Zuang, Zeev Berman, and certainly my old colleague Babis Karathanasis.

I would like to thank the Institute for Systems Research and the Electrical Engineering Department for the excellent resources and the stimulating research environment.

I wish to thank my loving wive Ioanna for her devotion, love and continuous assistance especially at the most difficult moments, that allowed me to pursue this work with pleasure. A special acknowledgment goes to my joyful son Nicholas, who is as old as this thesis. Also, I would like to thank my parents Nicholas and Vassiliki and my sister Pepi for their unlimited confidence and support since my early school years. I would like to take this opportunity to express my gratitude for two of the most inspiring teachers I have had the chance to

meet Ms Irini Iconomacou and Mr Dimitri Karandreas. Before I close, I certainly need to acknowledge the fellow greek students at UMCP and the Digenis association for making the past few years more enjoyable.

This research was supported in part by the National Science Foundation's Engineering Research Centers Program: NSFD CDR 8803012.

# TABLE OF CONTENTS

| <u>S</u> | ecti | <u>on</u> |                                   |   | Pa | ıge  |

|----------|------|-----------|-----------------------------------|---|----|------|

|          | List | of Tab    | oles                              |   |    | viii |

|          | List | of Fig    | ures                              | • |    | x    |

| 1        | Intr | oducti    | on                                |   |    | 1    |

|          | 1.1  | Histori   | ical Background and Motivation    |   |    | 1    |

|          | 1.2  | Proble    | m Identification and Contribution |   |    | 5    |

|          | 1.3  | Thesis    | Organization                      | • |    | 9    |

| 2        | Arc  | hitectu   | ıral Framework                    |   |    | 10   |

|          | 2.1  | Prelim    | inaries                           |   |    | 10   |

|          |      | 2.1.1     | Definitions                       |   | •  | 10   |

|          |      | 2.1.2     | Linear Time-Invariant Systems     |   |    | 11   |

|          | 2.2  | Design    | of a Time-Recursive Algorithm     |   |    | 13   |

|          |      | 2.2.1     | The Shift Property                |   |    | 13   |

|          |      | 2.2.2     | Time-Recursive Implementations    |   |    | 15   |

|          |      | 2.2.3     | On a Systematic Design I          |   |    | 18   |

|          |      | 2.2.4     | Mapping Operator Decomposition    |   |    | 19   |

|          |      | 2.2.5     | On a Systematic Design II         |   |    | 21   |

|          |      | 2.2.6     | The Difference Equation Property  |   |    | 22   |

|   | 2.3 | Design   | of a Time-Recursive Architecture                           | 23 |

|---|-----|----------|------------------------------------------------------------|----|

|   |     | 2.3.1    | Lattice Architecture Design for Mapping Operators          | 23 |

|   |     | 2.3.2    | The Periodicity Property                                   | 25 |

|   |     | 2.3.3    | IIR Architecture Based on the Shift Property               | 26 |

|   |     | 2.3.4    | IIR Architecture Based on the Difference Equation Property | 30 |

|   |     | 2.3.5    | IIR Architecture Design for Mapping Operators              | 32 |

|   | 2.4 | Impler   | nenting Sliding and Block Transforms                       | 33 |

|   | 2.5 | Conclu   | sion                                                       | 35 |

| 3 | Des | ign Pr   | ocedure                                                    | 37 |

|   | 3.1 | Generi   | c Design Procedure                                         | 37 |

|   | 3.2 | Examp    | ole A: Discrete Cosine Transform                           | 40 |

|   |     | 3.2.1    | SIMO Architecture for the Forward DCT                      | 40 |

|   |     | 3.2.2    | MISO Architecture for the Inverse DCT                      | 44 |

|   |     | 3.2.3    | Cost Issues                                                | 48 |

|   | 3.3 | Examp    | ole B: Discrete Fourier Transform                          | 53 |

|   |     | 3.3.1    | SIMO Architecture for the Forward DFT                      | 53 |

|   |     | 3.3.2    | MISO Architecture for the Inverse DFT                      | 54 |

|   |     | 3.3.3    | SIMO Architecture for the Inverse DFT                      | 58 |

|   |     | 3.3.4    | Cost Issues                                                | 59 |

|   |     | 3.3.5    | Cepstral Transform Architecture                            | 60 |

|   | 3.4 | Examp    | ole C: Discrete Wavelet Transform                          | 62 |

|   |     | 3.4.1    | Architecture for the DWT/IDWT                              | 63 |

|   |     | 3.4.2    | Cost Issues                                                | 66 |

|   | 3.5 | Conclu   | sion                                                       | 68 |

| 4 | App | plicatio | on on QMF Banks and Data Transforms                        | 70 |

|   | 4.1 | Unifor   | m-DFT Filter Banks                                         | 71 |

|   |     | 4.1.1    | Background                                                 | 71 |

|   |     | 4.1.2    | Time-Recursive IDFT in the Uniform-DFT Filter Bank .       | 74 |

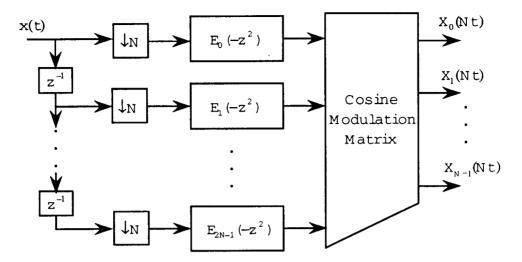

|   | 4.2 | Cosine   | Modulated Filter Banks                                     | 76 |

|   |     | 4.2.1    | Background                                                 | 76 |

|   |       | 4.2.2   | Time-Recursive Computation of the Cosine Modulation    |     |

|---|-------|---------|--------------------------------------------------------|-----|

|   |       |         | Matrix                                                 | 77  |

|   |       | 4.2.3   | Modified Implementation of the Cosine Modulated Filter |     |

|   |       |         | Bank                                                   | 78  |

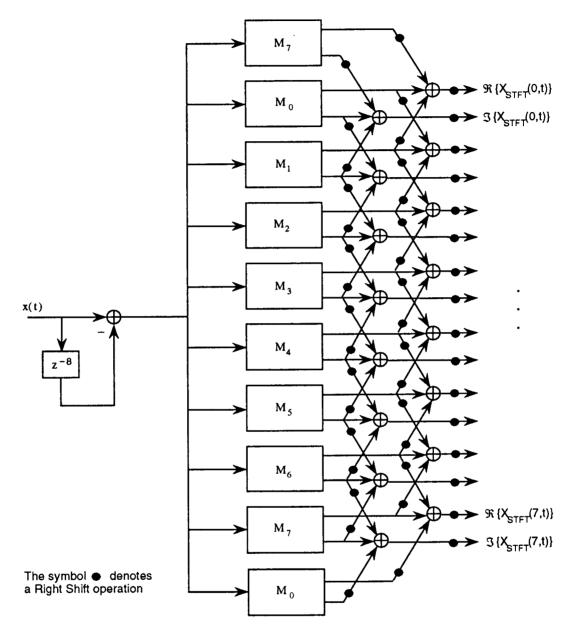

|   | 4.3   | Short   | Time Fourier Transform with Hanning Window             | 80  |

|   |       | 4.3.1   | Architecture for the STFT with Hanning window          | 81  |

|   |       | 4.3.2   | Cost Issues                                            | 83  |

|   | 4.4   | Modu    | lated Lapped Transform                                 | 85  |

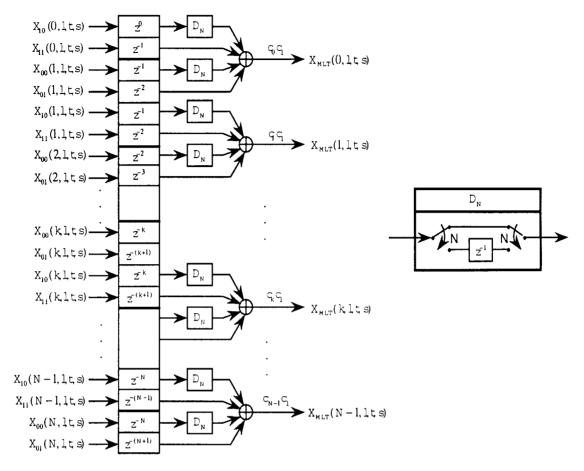

|   |       | 4.4.1   | Architecture for the Forward MLT                       | 86  |

|   |       | 4.4.2   | Architecture for the Inverse MLT                       | 88  |

|   |       | 4.4.3   | Cost Issues                                            | 92  |

|   | 4.5   | Exten   | ded Lapped Transform with Basis Length = $4N \dots$    | 92  |

|   |       | 4.5.1   | Architecture for the Forward ELT                       | 93  |

|   |       | 4.5.2   | Cost Issues                                            | 94  |

| 5 | An    | Exam    | ple in Processing of 2D Data                           | 96  |

|   | 5.1   | Algor   | ithm                                                   | 97  |

|   | 5.2   | Archi   | tecture                                                | 100 |

|   | 5.3   | Imple   | mentation Issues                                       | 103 |

| 6 | Cor   | nclusio | ns and Further Research                                | 104 |

| A | .ppe  | ndix A  | Proofs                                                 | 108 |

| R | Lefer | ences   |                                                        | 118 |

# LIST OF TABLES

| <u>Number</u> <u>P</u>                                                                                                                                                                                                                                                                                                                                   | age |

|----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----|

| 1.1 Implementation cost for sliding DFT                                                                                                                                                                                                                                                                                                                  | 3   |

| 1.2 Implementation cost for DFT                                                                                                                                                                                                                                                                                                                          | 4   |

| 2.1 Implementation cost of a mapping operator, based on a kernel group of size $M$ : Case a, the operator does not satisfy the periodicity property and it is utilized by a sliding transform. Case b, the operator satisfies the periodicity property and it is utilized by a sliding transform. Case c, the operator is utilized by a block transform. | 24  |

| 3.1 Cost metrics for the architectural implementation of block trans-                                                                                                                                                                                                                                                                                    |     |

| forms. $M_P$ , $A_P$ and $R_P$ denote the time delays associated with a bit-parallel implementation of the multiplier, the adder and the rotation circuit respectively. $M_S$ , $A_S$ and $R_S$ denote the corre-                                                                                                                                        |     |

| sponding time delays for a bit-serial implementation                                                                                                                                                                                                                                                                                                     | 49  |

| 3.2 Cost metrics (multiplication and addition counts) for the unipro-                                                                                                                                                                                                                                                                                    |     |

| cessor implementation of sliding transforms                                                                                                                                                                                                                                                                                                              | 49  |

| 3.3 Example of wavelet filter coefficients and the associated architec-                                                                                                                                                                                                                                                                                  |     |

| ture parameters.                                                                                                                                                                                                                                                                                                                                         | 66  |

| 4.1 | Cost metrics for the architectural implementation of block trans-     |    |

|-----|-----------------------------------------------------------------------|----|

|     | forms. $M_P, A_P$ and $R_P$ denote the time delays associated with a  |    |

|     | bit-parallel implementation of the multiplier, the adder and the      |    |

|     | rotation circuit respectively. $M_S, A_S$ and $R_S$ denote the corre- |    |

|     | sponding time delays for a bit-serial implementation                  | 84 |

| 4.2 | Cost metrics (multiplication and addition counts) for the unipro-     |    |

|     | cessor implementation of sliding transforms                           | 84 |

# LIST OF FIGURES

| Numb | Number                                                                 |      |  |

|------|------------------------------------------------------------------------|------|--|

| 1.1  | Pertain to the time-recursive computation                              | 3    |  |

| 2.1  | Lattice architecture for kernel group of size $M=2.\ldots$ .           | 15   |  |

| 2.2  | Architecture for kernel group of size $M = 1. \dots \dots$             | 18   |  |

| 2.3  | Lattice architecture for kernel group of size $M=3.\ldots$ .           | 24   |  |

| 2.4  | Part of lattice architecture if the periodicity property is satisfied. | 25   |  |

| 2.5  | IIR architecture for $M = 2$                                           | 29   |  |

| 2.6  | IIR architecture for $M=2$ if the periodicity property is satisfied.   | . 29 |  |

| 2.7  | IIR architecture for $M=3$ if the periodicity property is satisfied.   | . 29 |  |

| 2.8  | IIR architecture for $M=2$ for an operator used in block trans-        |      |  |

|      | form                                                                   | 35   |  |

| 2.9  | Lattice architecture for $M=2$ for an operator used in block           |      |  |

|      | transform.                                                             | 35   |  |

| 2.10 | Overview of the architecture design procedure                          | 36   |  |

| 3.1  | Architecture design procedure.                                         | 38   |  |

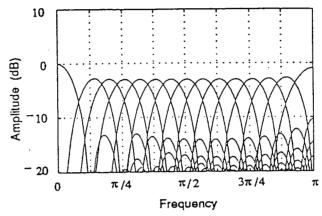

| 3.2  | The magnitude responses of the DCT filter bank for $N=16$ .            | 41   |  |

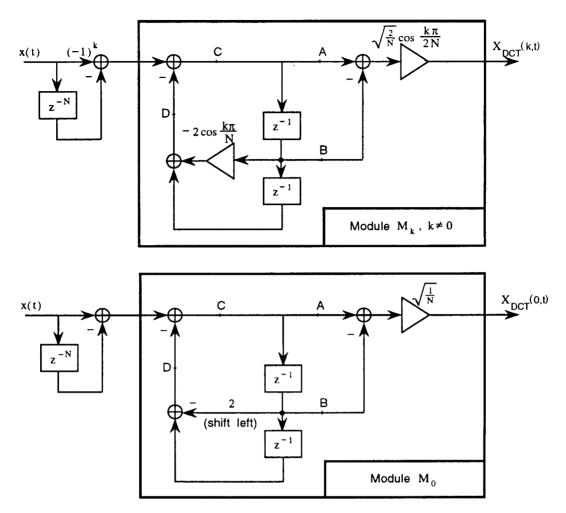

| 3.3  | IIR architecture for the DCT kernel function                           | 43   |  |

| 3.4  | Recursive architecture for the DCT                                     | 44   |  |

| 3.5  | Inverse transform module                                               | 47   |  |

| 3.6  | Recursive architecture for the IDCT                                    | 48   |  |

| 3.7  | Lattice architecture for the DFT module                          | 55  |

|------|------------------------------------------------------------------|-----|

| 3.8  | Recursive architecture for the DFT                               | 56  |

| 3.9  | IDFT module for complex input                                    | 57  |

| 3.10 | Details for real input IDFT module                               | 57  |

| 3.11 | Recursive architecture for the IDFT                              | 58  |

| 3.12 | Cepstral transform architecture based on fast logarithm circuit. | 61  |

| 3.13 | Cepstral transform architecture based on slow logarithm circuit. | 62  |

| 3.14 | The architectural modules used for DWT                           | 65  |

| 3.15 | Architecture for the DWT filters specified in table 3            | 67  |

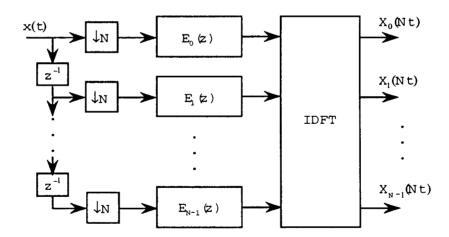

| 4.1  | N-channel QMF bank: a. analysis system, b. synthesis system.     | 72  |

| 4.2  | Typical frequency responses of uniform-DFT filters               | 72  |

| 4.3  | The uniform-DFT bank using polyphase decomposition               | 73  |

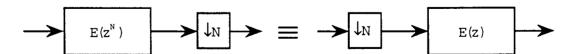

| 4.4  | The noble identity                                               | 73  |

| 4.5  | Decimated uniform-DFT bank using polyphase decomposition         |     |

|      | and time-recursive implementation for the IDFT                   | 75  |

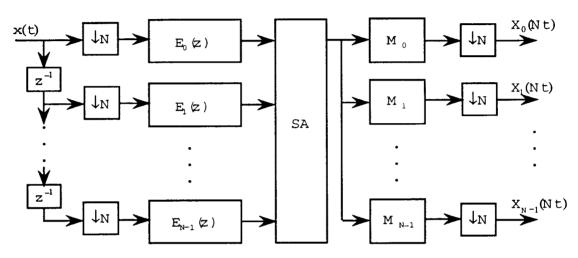

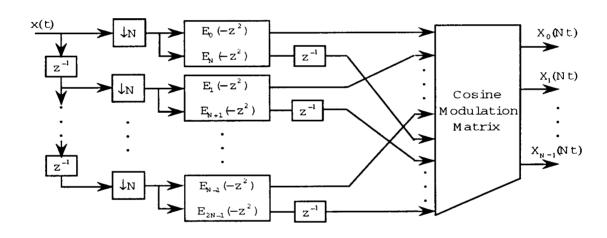

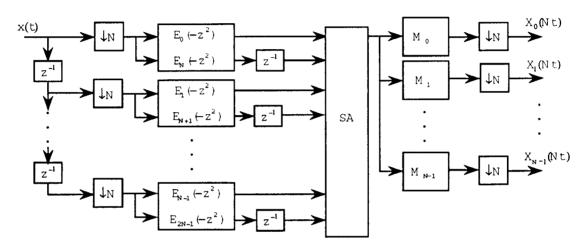

| 4.6  | QMF analysis bank based on cosine modulation                     | 77  |

| 4.7  | PR analysis bank based on cosine modulation                      | 77  |

| 4.8  | PR QMF analysis bank using time-recursive approach for imple-    |     |

|      | menting the cosine modulation matrix                             | 79  |

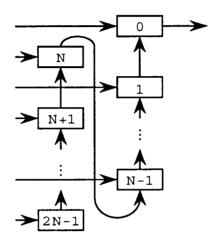

| 4.9  | The Shift Array (SA) used in the PR QMF structure                | 80  |

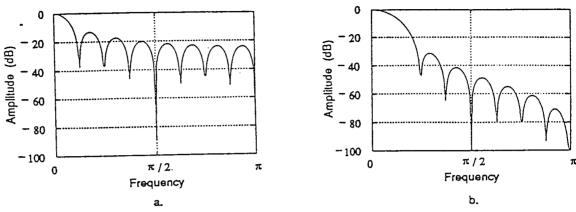

| 4.10 | The spectrum of a. the rectangular window and b. the Hanning     |     |

|      | window of length $N = 16$                                        | 81  |

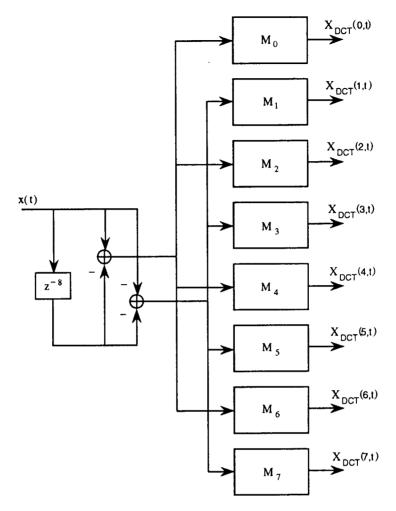

| 4.11 | Time-recursive architecture of the STFT for $N=8.\ldots$         | 83  |

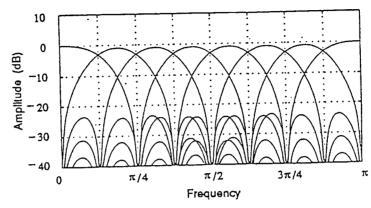

| 4.12 | The magnitude responses of the MLT filter bank for $N=8.$        | 86  |

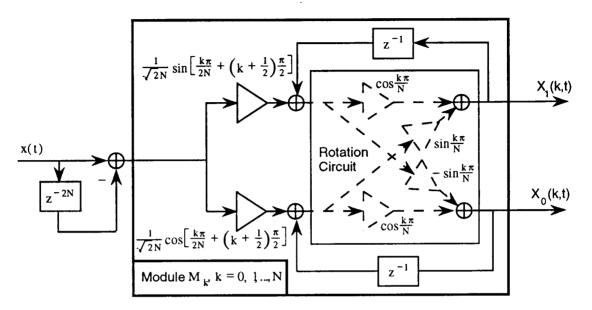

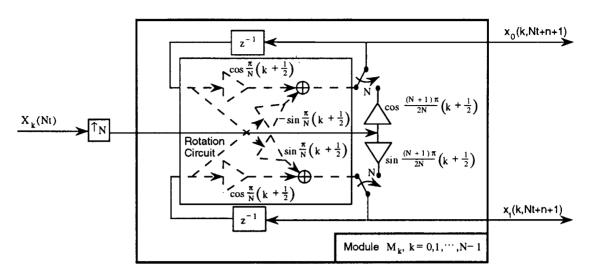

| 4.13 | Lattice architecture for the MLT module                          | 88  |

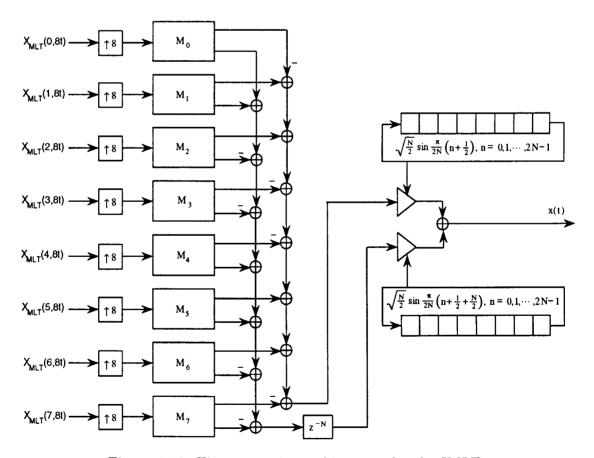

| 4.14 | Time-recursive architecture for the MLT                          | 89  |

| 4.15 | Lattice architecture for the IMLT module                         | 91  |

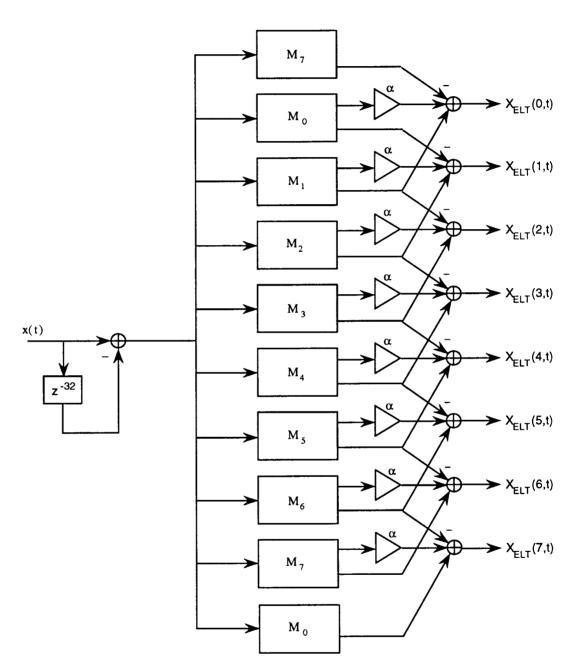

| 4.16 | Time-recursive architecture for the IMLT                         | 91  |

| 4.17 | Time-recursive architecture for the ELT                          | 95  |

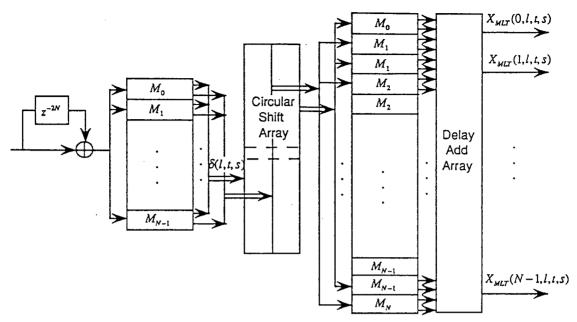

| 5 1  | Recursive architecture for the 2-D MLT                           | 100 |

| 5.2 | The Circular Shift Array: a. the architecture, b. the contents for |     |

|-----|--------------------------------------------------------------------|-----|

|     | the special case $N=4$                                             | 102 |

| 5.3 | The Delay Add Array.                                               | 103 |

Introduction

# 1.1 Historical Background and Motivation

Since the revolutionary publication by Cooley and Tukey [11] the fast Fourier transform (FFT) has been playing a key role in digital signal processing (DSP) in a wide range of applications, including transform coding, data filtering and spectral estimation [44, 51, 39]. Nevertheless, the increasing demand of processing huge volumes of data in real time, especially in audio, radar, sonar and video applications, suggests that the FFT-like fast algorithms (see for example [44, 59, 30, 36, 39, 48, 57]) may not be considered as the main building block in a number of modern DSP applications. The same is true for the VLSI architectures based on these algorithms. Three different reasons corroborate to this conjecture:

- Global Communication: The flow graphs of the FFT and the FFT-like fast algorithms exhibit a common structure composed of a series of log<sub>2</sub> N alternating butterfly interconnection and multiplier stages. The butterfly communication scheme requires global communication links if a parallel implementation is to be considered.

- Block Processing: The fast algorithms require buffering of blocks of data, and then block processing. This is not the natural way of processing for a number of applications such as audio, radar, sonar and video, where the input data are supplied in a sequential manner.

• Sliding Transform Computational Complexity: The FFT has been widely used for the transformation of windowed data, where the frequency content of the data is extracted for each displacement of a sliding window. This phenomenon appears in the transform domain adaptive filtering problem [12, 41, 43, 51]. The Discrete Fourier Transform used in such applications is referred to as the sliding DFT [51]. The FFT implementation of the sliding DFT requires the repetitive processing of neighboring data samples when the window slides.

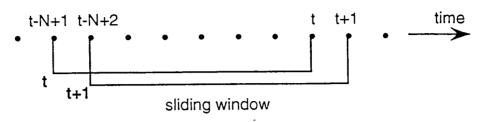

We can observe that the problem of computing the transform coefficients has appeared in two forms: in the first, one needs to compute the transform coefficients of the input data vector  $[x(t-N+1), x(t-N+2), \dots, x(t)]$  for each time instant  $t=0,1,\dots$ , where N is the size of a sliding window. In the second, one computes the above coefficients only at the time instants  $t=0,N,2N,\dots$ . For the sake of clarity throughout this thesis, we use the name sliding transform to describe the former situation and we reserve the term block transform for the latter one.

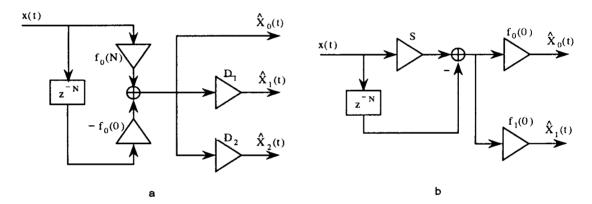

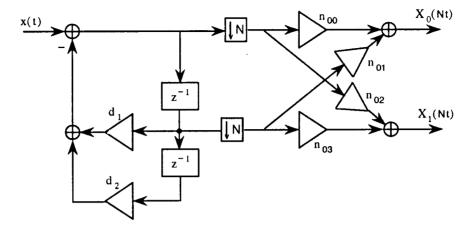

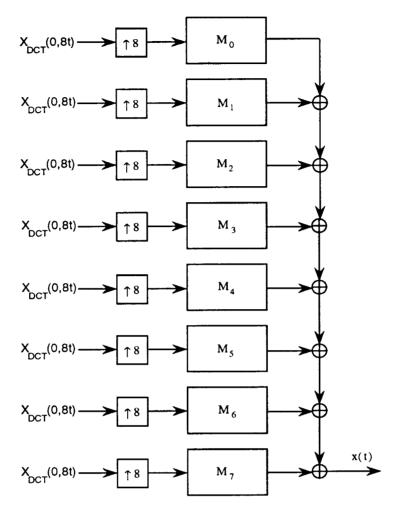

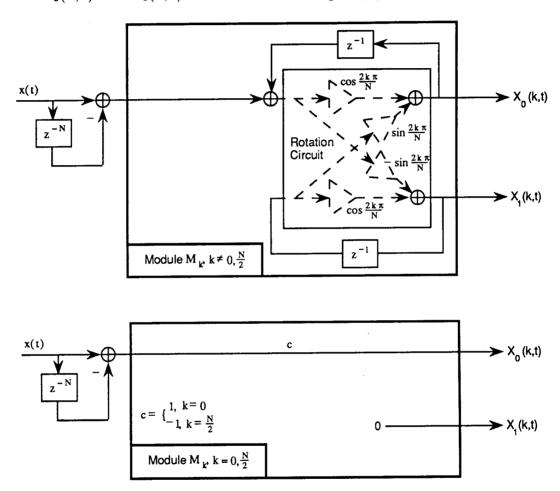

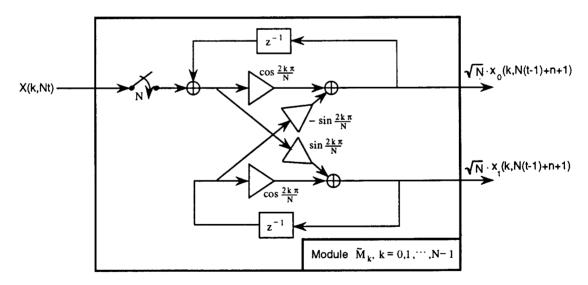

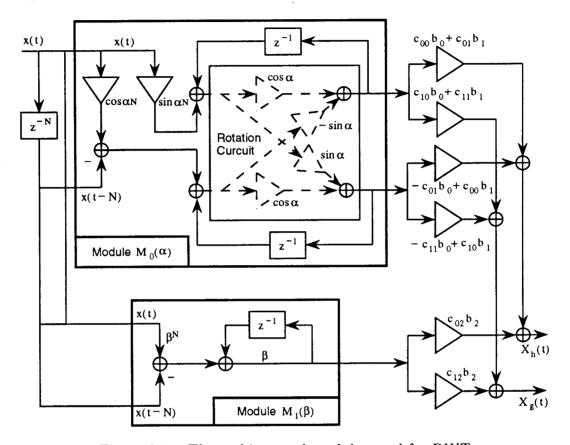

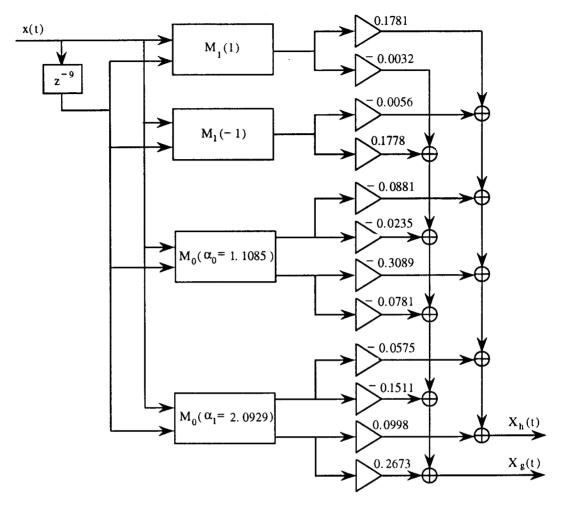

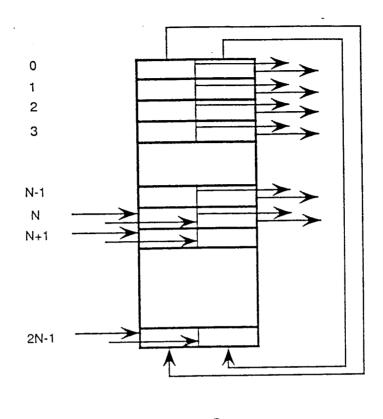

A number of authors have proposed a time recursive approach (either as a DSP programmable algorithm or VLSI architecture) for implementing sliding transforms in the context of the transform domain adaptive filtering, [7, 10, 42, 43, 61]. Within the time-recursive approach, the  $8 \times 8$  Discrete Cosine Transform is viewed as eight linear operators that function independently from each other: given a common input sequence they produce eight coefficient sequences. These frequency coefficients are evaluated at time instant t + 1 based on their values at time instant t and the input sample with time indices t - N + 1 and t + 1 (see Fig. 1.1). The motivation behind the time-recursive implementation of a sliding transform is the fact that the above update computation involves O(N) operations instead of  $O(N \log_2 N)$  implied in the FFT based implementations. This is reflected in the asymptotic cost expressions on Table 1.1  $^1$ .

<sup>&</sup>lt;sup>1</sup>The expressions under "throughput" denote the number of operations on the critical paths of the corresponding flow graphs that need to be carried out before the next block of data can be processed; in this case, before the window slides over the next position. A thorough

Time-recursive computation of sliding transforms has also found application in spectral analysis [32, 1] and frequency domain data filtering [47].

Figure 1.1: Pertain to the time-recursive computation.

|                         | parallel architecture criteria |                    |                 | uniprocesso    | r criteria    |

|-------------------------|--------------------------------|--------------------|-----------------|----------------|---------------|

|                         | operators                      | throughput         | communic.       | operations per | latency       |

|                         | -                              |                    |                 | output point   | per block     |

| direct                  | $O(N^2)$                       | O(N)               | local           | O(N)           | $O(N^2)$      |

| pipelined direct        | $O(N^2)$                       | O(1)               | local<br>giobal | O(log N)       | $O(N \log N)$ |

| FFT based pipelined FFT | $O(N \log N)$ $O(N \log N)$    | $O(\log N)$ $O(1)$ | global          | 0(10511)       | 0 (11 1551)   |

| time-recursive          | O(N)                           | 0(1)               | local           | O(1)           | O(N)          |

Table 1.1: Implementation cost for sliding DFT.

More recently, time-recursive designs have been successfully used in architectures for real-time computation of block transforms applied in data compression [9, 33, 34]. On Table 1.2, we display the asymptotic expressions of cost metrics used for the comparison of the time-recursive implementations with the FFT-like ones. Obviously, the algorithmic implementation of the FFT on a uniprocessor outperforms the corresponding one of the time-recursive implementation. At the architectural level though, the constant factors hidden by the asymptotic expressions are affected by the implementation details, thus leaving space for interesting cost trade-offs. The time-recursive implementation involves O(N) operators and local communication as opposed to  $O(N \log N)$  operators and global communication for a fully parallel and pipelined FFT architecture. In other words, less area and shorter internal clock cycle can by employed by

discussion on throughput requirements is pursued in Subsection 3.2.3.

the time-recursive architecture. A relevant asymptotic optimality result is formally proved in [34]. Note also that the locality property allows a bit-parallel implementation of the operators unlike the case of the architectures based on fast algorithms, where the global communication suggests a bit-serial implementation. Furthermore, the time-recursive architectures are very efficient for separable multi-dimensional data transforms. In particular, the implementation cost is linear in terms of the operators and the communication requirement remains local. The induction procedure for designing multi-dimensional architectures based on the one-dimensional ones is described in [34], while a detailed example is described in [9].

|                                 | parallel architecture criteria |                    |                 | uniprocessor   | criteria      |

|---------------------------------|--------------------------------|--------------------|-----------------|----------------|---------------|

|                                 | operators                      | throughput         | communic.       | operations per | latency       |

|                                 |                                |                    |                 | output point   | per block     |

| direct                          | $O(N^2)$                       | O(N)               | local           | O(N)           | $O(N^2)$      |

| pipelined direct<br>FFT based   | $O(N^2)$ $O(N \log N)$         | $O(1)$ $O(\log N)$ | local<br>global | O(log N)       | $O(N \log N)$ |

| pipelined FFT<br>time-recursive | $O(N \log N)$<br>O(N)          | O(1)<br>O(N)       | global<br>local | O(N)           | $O(N^2)$      |

Table 1.2: Implementation cost for DFT.

The subtle point in the time-recursive architectural implementation of the block transforms hinges on the fact that (as we will see in Chapter 2) the operators need to evaluate one result per time unit, while an operator in the fully parallel and pipelined FFT needs to produce one result every N time units (or equivalently, perform 1/N operation per time unit). The time unit is the time that lapses between two adjacent input data. Apparently, this is the reason that has discouraged the research and use of time-recursive computation for block transform implementation until recently [9, 33]. This situation has been changed due to the advances in VLSI technology that penalize more the global communication than the requirement for short internal clock cycle. As a side effect, the speed of a (VLSI implemented) operator can match the input data rate, by adjusting the length of the clock cycle. As long as this constraint is satisfied for a real-time application the area minimization becomes the only

concern in the design. Under this light, the success of the time-recursive VLSI circuits in computing block transforms and the promise they show are mainly justified, apart from the modularity, regularity and scalability of the resulted designs, by virtue of the area optimality property [34] and the communication locality property.

#### 1.2 Problem Identification and Contribution

We have seen in Section 1.1 that a number of time-recursive expressions have been used for implementing diverse computations in different application areas. Also, we have briefly explained why time-recursive computation can be expected to play a more dominant role in high throughput real-time applications in the near future. It is therefore very desirable to know what kind of computations can be carried out in an efficient manner by a time-recursive formulation, so that we can explore the full potential of the time-recursive computation model. Furthermore, one will question: given a computation in this class, does it translate to a unique architecture? If not, what are the alternatives and which is the best one? Can we derive this best architecture in an easy step-by-step, routine, or even automated way? Providing answers to the above questions, exploiting the implications in a number of real-time computation applications and revealing the common infrastructure of such computations in diverse areas constitutes the subject of the present thesis.

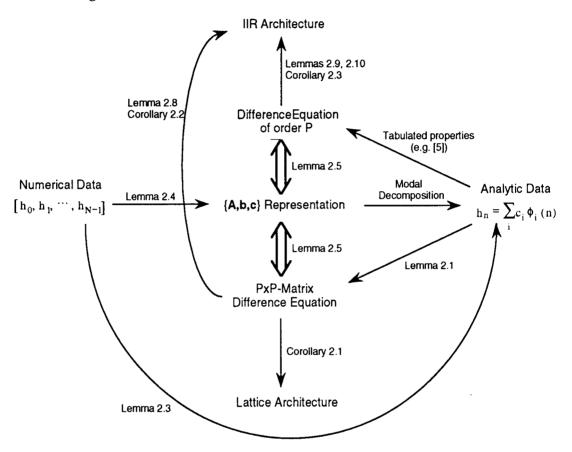

More specifically, we establish an architectural framework for parallel time-recursive computation. We consider a class of linear operators that is characterized by discrete time, time invariant, compactly supported, but otherwise arbitrary kernel functions. We introduce a **shift property** and show that this property underlies the time-recursive realization of the above operators. We show that the shift property dictates the parameter values of a parametric architectural structure, the **lattice structure**, that is a generalization of the structure that has appeared in the literature with the same name (see [9, 33, 42]). We show that the information carried by the shift property is equivalent to the

information carried by the parameters of a linear difference equation. The latter is a generalization of the order-2 difference equation introduced in [34] and it dictates an IIR structure for the time-recursive architecture. We introduce a periodicity property and show how it affects the choice among the lattice and the IIR architecture, as well as the complexity of the architecture itself. We show that an arbitrary mapping operator can be implemented in a time-recursive way and we provide an optimal implementation (in the class of time-recursive implementations). We conclude that given a mapping operator the efficiency of the time-recursive architecture depends on the eigenfunctions of an appropriate Linear Time Invariant (LTI) system.

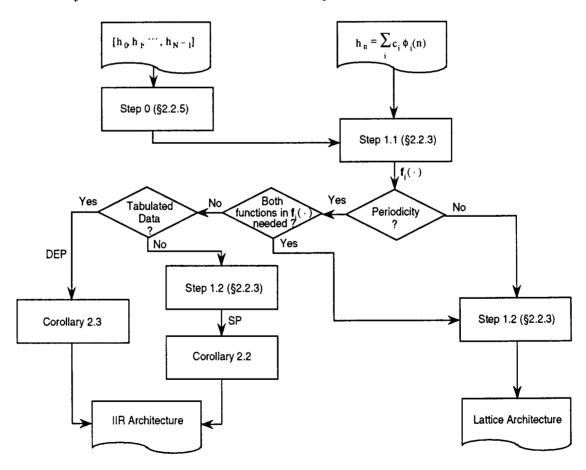

Based on the above analysis, we obtain the flow graph of a design procedure that routinely produces the time-recursive architecture for a specified mapping operator. This design procedure can also be viewed as the back bone of a CAD tool that can take a high level description of a computation (for example an algebraic formula) and produce VLSI layout for the appropriate time-recursive architecture. The efficiency and potential of this design procedure is demonstrated by means of specific design examples: the Discrete Cosine Transform (DCT) [34], the Discrete Fourier Transform (DFT) [32] and the Discrete Wavelet Transform (DWT) [2]. Furthermore, the architecture design of the Short Time Fourier Transform with Hanning windowing is demonstrated. Among the above, the inverse DCT we propose, the DWT and the inverse DWT are novel designs.

A brief description of four more advanced designs follows:

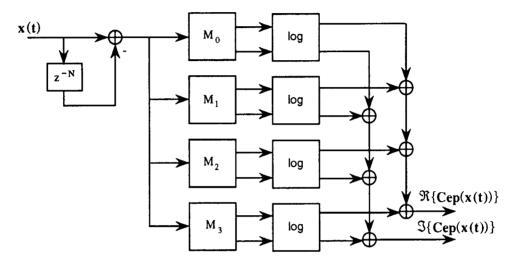

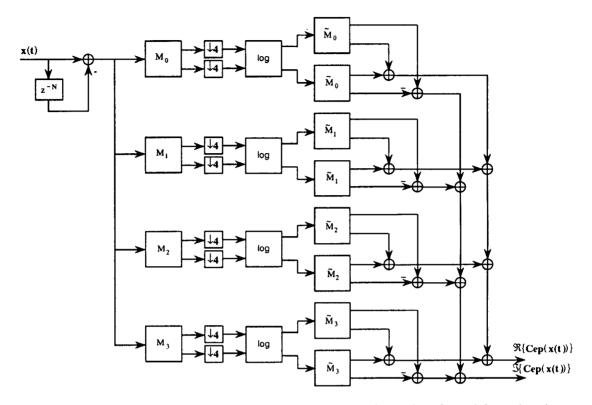

1. Cepstral Transform: The size-N complex Cepstral transform  $y(t), t = 0, 1, \cdots$  of a real valued sequence  $x(t), t = 0, 1, \cdots$  is defined as [46]

$$y(t) = IDFT\{\log(DFT\{x(t)\})\}, \quad t = 0, 1, \dots,$$

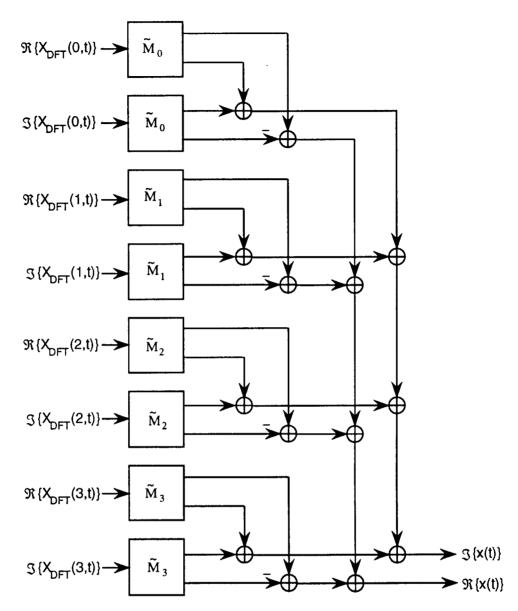

where IDFT denotes the inverse DFT. The architectural implementation involves two fast Fourier transforms and a bank of logarithm circuits. We propose two architectures for the Cepstral transform, in which we implement DFT and IDFT in a time recursive way. We are not concerned about

the implementation details of the logarithm circuits, nevertheless we are concerned about the speed of this circuit. In the first architecture, we assume that logarithm circuits which can perform one operation per time unit are available. The cost of the resulted time-recursive architecture is 3N-1 adders, N-2 rotation circuits, and N "fast" logarithm circuits. In the second one, we assume that the logarithm circuits can perform one operation every N time units. In this case, the resulted cost is 6N-1 adders, 3N-6 rotation circuits and N "slow" logarithm circuits. Both designs may employ very efficient rotation circuits [52].

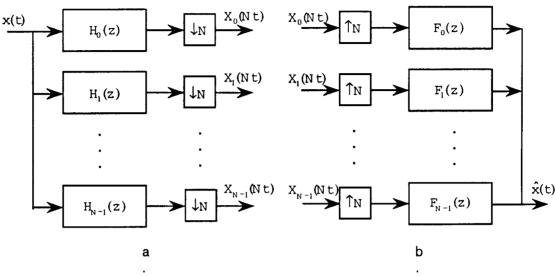

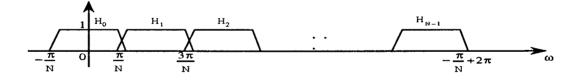

- 2. N-Band Modulated Quadrature Mirror Filter (QMF) bank: There are two common versions of the modulated QMF bank [54]: the uniform-DFT QMF bank and the cosine modulated QMF bank. They both find applications in audio data processing and they enjoy substantial advantages over alternative designs of both Perfect Reconstruction (PR) QMF banks and pseudo QMF banks [54]. In particular, they are easier both to design and to implement. The cosine modulated QMF bank has the additional advantage that given a real input sequence the produced output is also real. These filter banks are implemented by using the polyphase components of a prototype filter [54, 39] followed by a transform matrix. The latter is the  $N \times N$  IDFT matrix for the case of the uniform-DFT QMF and a  $N \times 2N$  matrix of cosines for the case of the cosine modulated QMF. These matrices are typically implemented by fast algorithm techniques that require global communication. Here, we propose the substitution of the fast algorithm implementation by using a time-recursive approach. The resulting circuits involve only local communication, while the cost of the modulation matrices becomes linear.

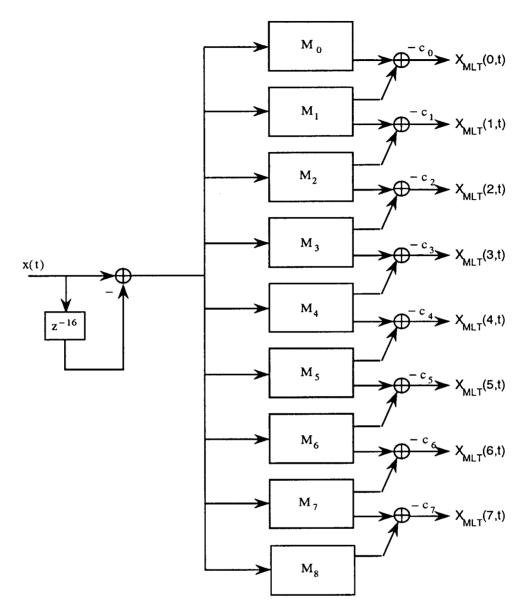

- 3. One-Dimensional Lapped Transforms: The Modulated Lapped Transform (MLT) operates on data segments of length 2N, x(t + n 2N + 1),  $n = 0, 1, \dots, 2N 1$  and it produces N output coefficients  $X_k(t)$ , k = 1

$0, 1, \dots, N-1$  as follows [36]:

$$X_{k}(t) = c_{k} \sqrt{\frac{2}{N}} \sum_{n=0}^{2N-1} \sin \frac{\pi}{2N} \left( n + \frac{1}{2} \right) \cos \left[ \frac{\pi}{N} \left( k + \frac{1}{2} \right) \left( n + \frac{1}{2} + \frac{N}{2} \right) \right]$$

$$x(t+n-2N+1),$$

where  $t = 0, 1, \dots$  and  $c_k = (-1)^{(k+2)/2}$  for even k and  $c_k = (-1)^{(k-1)/2}$  for odd k. The MLT is a special case of PR cosine modulated QMF bank, where the polyphase components mentioned above are FIR filters of length equal to 2. The MLT has been proved very useful in audio data coding because it alleviates the blocking effect [36]. Here, we propose a time-recursive implementation of the MLT. The implied cost is 2N + 3 multipliers, 3N + 3 adders and N - 1 rotation circuits.

Furthermore, we design a circuit for an Extended Lapped Transform (ELT) with basis function length equal to 4N [38]. This ELT is equivalent to a PR cosine modulated QMF bank with polyphase components of length 4. The implementation cost is 3N + 4 multipliers, 4N + 4 adders and N + 2 rotation circuits.

We would like to highlight the importance of these results by mentioning that the MLT and ELT have been incorporated by the ISO-MPEG and ASPEC standards for audio coding with the name Modified DCT (MDCT).

4. Two-dimensional MLT: The 2D MLT is used for image data coding. Compared to 2D DCT, at the same coding rate it implies considerably less blocking effect and slightly higher Signal to Noise Ratio [39]. Here, we propose the time-recursive implementation of the 2D MLT, for which we need three one-dimensional MLT circuits, with an overhead of shift registers and linear number of adders. The resulting design is modular, regular, scalable and it requires local communication.

All of the above designs are original and are the best known to date in terms of operator counts.

Although throughout the thesis we focus on architectural implementations for either sliding transforms or block transforms, the designs we present are useful for algorithmic implementations of sliding transforms too.

## 1.3 Thesis Organization

In this thesis, we establish a framework for parallel time-recursive computation, we explain the subtle points by means of specific examples and we propose novel designs for some important real-time computations.

In Chapter 2, we expose the main ideas of the time-recursive computation, we derive the various representations of a time-recursive computation and we generate the basic architectural structures that will serve as the building modules in later chapters.

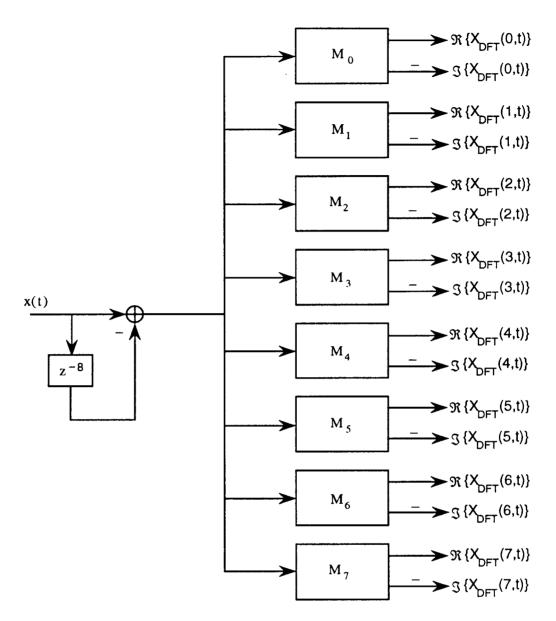

In Chapter 3, we introduce a generic design procedure for time-recursive architectures and explain its use by designing architectures for the Discrete Fourier Transform (DFT), the Discrete Cosine Transform (DCT) and a dyadic Discrete Wavelet Transform (DWT). Furthermore, based on the DFT architecture, we propose a novel design for the Cepstral Transform.

In Chapter 4, we consider a number of problems related to modulated QMF banks: introducing the time-recursive computation in the uniform-DFT QMF bank and the cosine modulated bank, implementing the Short Time Fourier Transform (STFT) with a non-rectangular window, the one-dimensional Modulated Lapped Transform (MLT) and an Extended Lapped Transform (ELT).

In Chapter 5, we derive the architecture of the two-dimensional MLT.

In Chapter 6, we summarize the results of this dissertation and we suggest some directions for future research.

In Appendix A, we give the proofs of some lemmas that are stated in the course of our presentation.

#### **Architectural Framework**

In this Chapter, we exploit the structure underlying time-recursive computation and we use this knowledge to construct the tools necessary for a systematic design of time-recursive architectures.

In Section 2.1, we introduce some terminology that will be used throughout the thesis. Also, for easy reference, we highlight some principles from linear systems theory. In Section 2.2, we study the time-recursive algorithmic structures and their properties. In Section 2.3, we focus on the architectural implementation of time-recursive architectures. In Section 2.4, we briefly discuss the special features pertinent to block data transforms. We conclude with Section 2.5.

## 2.1 Preliminaries

#### 2.1.1 Definitions

In many signal processing applications the key computation consists of a mapping operator  $[h_0 \ h_1 \ \cdots \ h_{N-1}] : x(\cdot) \to X(\cdot)$ , which operates on the semiinfinite sequence of scalar data  $x(\cdot)$  and produces the sequence  $X(\cdot)$  as follows:

$$X(t) = \sum_{n=0}^{N-1} h_n x(t+n-N+1), \quad t = 0, 1, \cdots.$$

(2.1.1)

Note that all FIR filters can be considered as this type of computation. This is also true for a number of data transforms. For example, the  $k^{\text{th}}$  frequency component of the N-point Discrete Fourier Transform (DFT) is obtained for

$$h_n = e^{-\frac{2\pi j}{N}kn}$$

We can specify a mapping operator  $[h_0 \ h_1 \ \cdots \ h_{N-1}]$  with a function  $f(\cdot)$ , for which the values at the points  $0, 1, \cdots, N-1$  are the prescribed coefficients:  $h_n = f(n), \ n = 0, 1, \cdots, N-1$ . In the sequel, we will use the term **kernel function** or simply **kernel** for this function  $f(\cdot)$ . For example, the kernel f(n) = 1 is associated to the mapping operator  $[h_n = 1, n = 0, 1, \cdots, N-1]$  and similarly, the kernel  $f(n) = e^{\alpha n}$  is associated to the operator  $[e^{\alpha n}, n = 0, 1, \cdots, N-1]$ . Furthermore, we will call **kernel group** a vector of kernel functions  $f_0(\cdot), f_1(\cdot), \cdots, f_{M-1}(\cdot)$

$$\mathbf{f}(\cdot) = \left[ f_0(\cdot) \ f_1(\cdot) \ \cdots \ f_{M-1}(\cdot) \right]^T.$$

A time-recursive implementation of a mapping operator  $[h_n \ h_1 \ \cdots \ h_{N-1}]$  is the one that is based on an update computation of the type

$$X(t+1) = \mathcal{U}(X(t), x(t-N+1), x(t+1)).$$

For example, if we have  $[h_n = 1, n = 0, 1, \dots, N-1]$ , X(t) will be the sum of the last N values in the input stream. The time-recursive algorithmic implementation of this operator will simply be the computation

$$X(t+1) = X(t) + x(t+1) - x(t-N+1).$$

# 2.1.2 Linear Time-Invariant Systems

In this Section, we make a brief review of some basic concepts from the linear system theory. This will be helpful for a better understanding of the material in Chapter 2. For a comprehensive presentation of these concepts the reader may refer to [27].

A single-input single-output discrete-time Linear Time Invariant (LTI) system of order M can be described by the state space equations

$$\mathbf{x}(n+1) = \mathbf{A}\mathbf{x}(n) + \mathbf{b}u(n)$$

$$y(n) = \mathbf{c}\mathbf{x}(n),$$

where  $\mathbf{x}(\cdot)$  is the length-M state vector and  $u(\cdot), y(\cdot)$  are the input and output variables respectively. Also,  $\mathbf{A}$  is the  $M \times M$  system matrix, while  $\mathbf{b}$  is a length-M column vector and  $\mathbf{c}$  is a length-M row vector.  $\{\mathbf{A}, \mathbf{b}, \mathbf{c}\}$  is an order- $\mathbf{M}$  state space description of the LTI system and it provides information for both the input/output behavior and the internal structure of the system.

The quantities

$$h_n = \mathbf{c} \mathbf{A}^n \mathbf{b},\tag{2.1.2}$$

$n=0,1,\cdots$ , are the Markov parameters of the linear system and they are sufficient to describe completely the input/output (i/o) behavior of this system. Consequently, providing an i/o description for a system is equivalent to providing the Markov parameters, while the state space description for this system is non-unique.

Two different order-M state space descriptions that yield a common i/o behavior are related with a similarity transformation specified as follows

$${\mathbf A}, {\mathbf b}, {\mathbf c} \longrightarrow {\mathbf T}^{-1} {\mathbf A} {\mathbf T}, \ {\mathbf T}^{-1} {\mathbf b}, {\mathbf c} {\mathbf T} \},$$

where **T** is an invertible  $M \times M$  matrix. One can easily verify that the transformed state space description has the same Markov parameters with the original one.

There is a number of standard state space description forms. Two of the most commonly used ones are:

#### 1. Controller canonical form: A and b are in the form

$$\mathbf{A} = \begin{bmatrix} -\alpha_1 & -\alpha_2 & \cdots & -\alpha_{M-1} & -\alpha_M \\ 1 & 0 & \cdots & & 0 \\ 0 & 1 & & & \\ \vdots & \ddots & \ddots & & \vdots \\ 0 & 0 & 1 & 0 \end{bmatrix}, \qquad \mathbf{b} = \begin{bmatrix} 1 \\ 0 \\ 0 \\ \vdots \\ 0 \end{bmatrix}, \quad (2.1.3)$$

while  $\alpha_1, \alpha_2, \dots, \alpha_M$  are non-zero parameters. The output vector  $\mathbf{c}$  does

not have any specific structure.

2. Modal canonical form: Let  $\beta_i e^{\pm \alpha_i}$ ,  $i = 0, 1, \dots, I$  be the eigenvalues of the system matrix **A** in polar representation. Note that for real eigenvalues we have  $\alpha_i = 0$ . A linear system is in modal canonical form if the system matrix **A** is block diagonal with block elements in the form

$$\beta_i \begin{bmatrix} \cos \alpha_i & \sin \alpha_i \\ \cos \alpha_i & -\sin \alpha_i \end{bmatrix}$$

.

The above reduces to  $\beta_i$  if  $\alpha_i = 0$ .

Given the Markov parameters  $h_0, h_1, \dots$ , of an LTI system a state space description  $\{\mathbf{A}, \mathbf{b}, \mathbf{c}\}$  of order M specifies a minimal order realization if (2.1.2) holds with  $n = 0, 1, \dots$  and furthermore (2.1.2) does not hold for any state space realization of order M - 1.

Given the Markov parameters  $h_0, h_1, \dots, h_{N-1}$ , of an LTI system, a state space description  $\{\mathbf{A}, \mathbf{b}, \mathbf{c}\}$  of order M specifies a minimal order partial realization if (2.1.2) holds with  $n = 0, 1, \dots, N-1$  and furthermore it does not hold for any state space description of order M-1. The problem of finding a minimal order partial realization is addressed in detail in [29]. An illustrative example is discussed in [27, pp.491-492].

# 2.2 Design of a Time-Recursive Algorithm

# 2.2.1 The Shift Property

In the course of our study we will see that all mapping operators specified in (2.1.1) can be implemented in a time-recursive way. Nevertheless, the implementation cost not always justifies the time-recursive computation. In the following Lemma, we specify a family of kernels and kernel groups that can be implemented time-recursively in a way that will be determined shortly.

Shift Property: A kernel group  $\mathbf{f}(\cdot) = [f_0(\cdot) \ f_1(\cdot) \ \cdots \ f_{M-1}(\cdot)]^T$ , satisfies the

shift property (SP) if it satisfies the (matrix) difference equation

$$\mathbf{f}(n-1) = \mathbf{R}\mathbf{f}(n), \quad n = 1, 2, \dots, N,$$

(2.2.1)

with a specified final condition f(N), where R is a constant matrix of size  $M \times M$ . Furthermore, we will say that a kernel function  $\phi(\cdot)$  satisfies SP if there is a kernel group  $f(\cdot)$  that satisfies SP and  $\phi(\cdot)$  is an element of  $f(\cdot)$ .  $\square$

**Lemma 2.1** A time-recursive implementation of a kernel group  $f(\cdot)$  is feasible if this kernel group satisfies the shift property.

**Proof:** (2.2.1) gives:

$$f_p(n-1) = \sum_{q=0}^{M-1} r_{pq} f_q(n), \quad n = 1, 2, \dots, N, \quad p = 0, 1, \dots, M-1,$$

where  $r_{pq}, p, q = 0, 1, \dots, M-1$  are the elements of the matrix **R**. Let

$$X_p(t) = \sum_{n=0}^{N-1} f_p(n)x(t+n-N+1), \quad p = 0, 1, \dots, M-1$$

(2.2.2)

Suppose this is available at the time instant t+1. For the quantities  $X_p(t+1)$ ,  $p=0,1,\dots,M-1$  we have:

$$X_p(t+1) = \sum_{n=0}^{N-1} x(t+n+1-N+1)f_p(n) = \sum_{n=1}^{N} x(t+n-N+1)f_p(n-1)$$

$$= \sum_{n=1}^{N} x(t+n-N+1) \sum_{q=0}^{M-1} r_{pq} f_q(n) = \sum_{q=0}^{M-1} r_{pq} \left( \sum_{n=1}^{N} x(t+n-N+1) f_q(n) \right)$$

and therefore we obtain the algorithm:

$$X_p(t+1) = \sum_{q=0}^{M-1} r_{pq} \left[ X_q(t) - x(t-N+1) f_q(0) + x(t+1) f_q(N) \right], \qquad (2.2.3)$$

where  $p=0,1,\dots,M-1$ . If we assume knowledge of the boundary values  $\{f_q(0),f_q(N),\ q=0,1,\dots,M-1\}$ , the algorithm specified in (2.2.3) will become the update computation we were after. (2.2.1) implies that knowledge of  $\mathbf{f}(N)$

yields  $\mathbf{f}(0)$ . Furthermore, note that if  $\mathbf{R}$  is nonsingular, knowledge of  $\mathbf{f}(0)$  yields  $\mathbf{f}(N)$ .

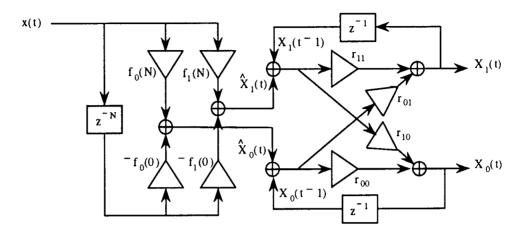

Figure 2.1: Lattice architecture for kernel group of size M = 2.

Corollary 2.1 A kernel group  $f(\cdot)$  that satisfies SP can be implemented time-recursively as follows:

- 1. Compute the matrix **R** by evaluating f(n-1) and using (2.2.1).

- 2. Evaluate f(n) at the points n = 0 and n = N.

- 3. At each time instant t evaluate (2.2.3).  $\square$

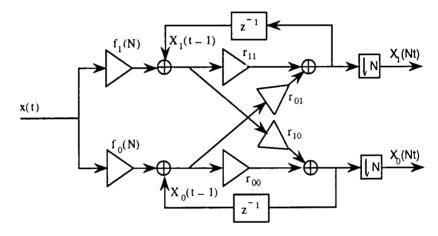

Note that the first two steps of the above algorithm belong to the initialization phase (off-line computation). The architectural implementation will have a lattice structure if the size of the kernel group is M=2 (see Fig. 2.1). An example of this architecture appears in [33]. In an abuse of terminology, we will call lattice architectures the architectures that implement (2.2.3) regardless of the size of the kernel group.

# 2.2.2 Time-Recursive Implementations

The issue of specifying a family of kernel groups that satisfy SP is addressed by Lemma 2.2:

Lemma 2.2 The shift property is satisfied by:

- 1. The singleton kernel group  $[cb^n]$ , where b and c are non-zero free parameters.

- 2. The kernel group  $[c_{00}b^n + c_{01}b^{-n}, c_{10}b^n + c_{11}b^{-n}]^T$ , where b is a non-zero parameter and the coefficients are free parameters, such that  $c_{00}c_{11} c_{01}c_{10} \neq 0$ .

- 3. The kernel group  $\left[c_0, c_1 n, \cdots, c_{M-1} n^{M-1}\right]^T$ , where the coefficients are non-zero parameters.

- 4. The union of two kernel groups that satisfy SP.

- 5. The cartesian product of two kernel groups that satisfy SP. □

The proof of this Lemma can be found in the Appendix.

Suppose now that we are given a mapping operator  $[h_0 \ h_1 \ \cdots \ h_{N-1}]$  for which we have the following linear decomposition:

$$h_n = \alpha \phi(n) + \beta \psi(n), \quad n = 0, 1, \dots, N - 1,$$

and  $\phi(\cdot)$ ,  $\psi(\cdot)$  are kernel functions that satisfy SP. One may verify that  $h_n$  can not be proved to satisfy SP based on the above linearity property. Nevertheless, we have

$$X(t) = \sum_{n=0}^{N-1} h_n x(t+n-N+1) = \sum_{n=0}^{N-1} \left[\alpha \phi(n) + \beta \psi(n)\right] x(t+n-N+1)$$

$$= \alpha \left[ \sum_{n=0}^{N-1} \phi(n) x(t+n-N+1) \right] + \beta \left[ \sum_{n=0}^{N-1} \psi(n) x(t+n-N+1) \right] \quad \text{or}$$

$$X(t) = \alpha X_{\phi}(t) + \beta X_{\psi}(t),$$

where  $X_{\phi}(t)$  and  $X_{\psi}(t)$  have the obvious definitions. Therefore, we can obtain an efficient time-recursive implementation for the linear combination of two (or more) kernels that satisfy SP, by properly combining the output points of the implementations of the latter. The mapping operators generated by this linearity property supplement the family of the operators that can be computed in a recursive way based on Lemma 2.2.

Now we will discuss some of the most interesting examples of the timerecursive computation, under the light of Lemma 2.2.

- 1. We may observe that for b=c=1 the kernel group in Lemma 2.2, Statement 1 specifies the mapping operator that computes the sum of the last N values in the input stream.

- 2. If  $b = e^{j2k\pi/N}$ , and c = 1 the same case of kernel group specifies the  $k^{\text{th}}$  frequency component of the DFT. From Fig. 2.2, we conclude that the recursive implementation requires one complex multiplier. Consequently, no more than N complex multipliers are required for the computation of the N point DFT. This result was obtained in [47, pp.175-179] and [7]. It was rediscovered and used in the real-time architecture context in [32], where it is also pointed out that N rotation circuits [52] suffice for the computation of the DFT.

- 3. Another interesting special case of kernel group is obtained from Lemma 2.2, Statement 2 for

$$\begin{bmatrix} c_{00} & c_{01} \\ c_{10} & c_{11} \end{bmatrix} = \begin{bmatrix} \frac{1}{2}e^{j\frac{k\pi}{2N}} & \frac{1}{2}e^{-j\frac{k\pi}{2N}} \\ \frac{1}{2j}e^{j\frac{k\pi}{2N}} & \frac{1}{2j}e^{-j\frac{k\pi}{2N}} \end{bmatrix} \quad \text{and} \quad b = e^{j\frac{k\pi}{N}}.$$

(2.2.4)

For this choice of our constants we obtain  $f_0(n) = \cos \frac{k\pi}{N}(n+\frac{1}{2})$  and  $f_1(n) = \sin \frac{k\pi}{N}(n+\frac{1}{2})$ . One can recognize the kernels of the DCT and the DST. The algorithm for computing the DCT/DST in a time-recursive manner was proposed by [61] and was suggested for the sliding transform computation. In [33] it was realized that time-recursiveness results an efficient architectural design for the DCT/DST. It was shown that such an implementation requires less than 6N real multipliers.

4. The fact that the kernel group in Lemma 2.2, Statement 3 can be implemented time-recursively was independently observed in [16] and in [1],

where it is used for estimating the energy spectral density of a noisy waveform via Taylor series.

5. One can use Lemma 2.2, Statement 5 in order to design a lattice architecture for the Lapped Orthogonal Transform (LOT) [36, 38, 39, 62]. The feasibility of such a design is due to the fact that some LOT kernel functions are products of two sinusoidal kernels. The time-recursive implementation of the LOT first appeared in [34]. The implementation of two interesting special cases of the LOT, the Modulated Lapped Transform (MLT) [36] and an Extended Lapped Transform (ELT) [38] are considered in detail in Chapter 4.

Figure 2.2: Architecture for kernel group of size M = 1.

## 2.2.3 On a Systematic Design I

Surprisingly, we can realize that:

**Lemma 2.3** Every mapping operator of finite length N can be implemented in a time-recursive way.  $\square$

The proof is given in the Appendix.

A reasonable question follows from this existence result regarding the timerecursive implementation of a given mapping operator. We will proceed with a design procedure that partially answers this question. To do so we will make the assumption that a given operator can be expressed by inspection (and use of Lemma 2.2) as a linear combination of kernel functions that satisfy SP. For example, the kernel functions of the discrete sinusoidal transforms belong in this class of operators (cf. Lemma 2.2, Statement 2).

## Design Procedure

## Input:

$$h_n = \sum_{i} c_i \phi_i(n), \qquad (2.2.5)$$

where  $\{\phi_i(n)\}\$  is a set of kernel functions that satisfy the shift property SP and  $\{c_i\}$  is a set of known constants.

## Step 1.1:

Specify the kernel groups  $\mathbf{f}_i(\cdot)$  to which the kernel functions  $\phi_i(\cdot)$  belong. For example, if  $\phi_i(n) = n^2$  then, according to Lemma 2.2, Statement 3, we get  $\mathbf{f}_i(n) = \begin{bmatrix} 1 & n & n^2 \end{bmatrix}^T$ .

#### Step 1.2:

For each kernel group  $\mathbf{f}_i(\cdot)$  use (2.2.1) in order to compute the matrix of parameters  $\mathbf{R}_i$  and evaluate  $\mathbf{f}_i(n)$  at the points n=0 and n=N.

The outcome of this design procedure is the following algorithm:

- 1. Evaluate (2.2.3) in order to obtain  $X_i(t)$ , defined as  $X_i(t) = \sum_{n=0}^{N-1} \phi_i(n)x(t+n-N+1)$ .

- 2. Evaluate

$$X(t) = \sum_{i} c_{i} X_{i}(t). \tag{2.2.6}$$

The kernel group associated to the mapping operator is the union  $\bigcup_i \mathbf{f}_i(\cdot)$ .  $\square$  Detailed examples along the lines of this procedure are given in later Chapters.

# 2.2.4 Mapping Operator Decomposition

In Subsection 2.2.3 we introduced a design procedure for the time-recursive implementation of a class of mapping operators. In this class, the operator coefficients are specified in by a close form description that can be manipulated easily by inspection and compared to the kernel functions in Lemma 2.2. If this

is not feasible, an elaborate technique must be employed to obtain the linear expression required as the input of the design procedure. This is the subject of this Subsection.

One can easily verify that for a given mapping operator a number of different recursive architectural implementations exist. Given a mapping operator, we would like to obtain the optimal time-recursive implementation in terms of the architectural cost. Unfortunately, this is not an easy problem, since a variety of ad-hoc designs may exist for a specified operator. Here, we address the question of optimality with respect to the number of kernels that are used in a linear decomposition of the given mapping operator. We show that this question is equivalent to finding the minimal order partial realization of a proper linear time-invariant (LTI) system. With this approach, we do not assume any prior knowledge of the structure of the coefficients of the given operator.

**Lemma 2.4** The size of the smallest kernel group that can be used to implement the mapping operator  $[h_0 \ h_1 \ \cdots \ h_{N-1}]$  in a time-recursive way is equal to the size of the minimal order partial realization of the LTI system with the N first Markov parameters being equal to the coefficients of the specified operator.

**Proof:** Given a mapping operator  $[h_0 \ h_1 \ \cdots \ h_{N-1}]$ , we can have the following coefficient expansion:

$$h_n = \mathbf{c} \mathbf{A}^n \mathbf{b}, \quad n = 0, 1, \dots, N - 1,$$

(2.2.7)

where **A** is the system matrix of size  $M \times M$  and **b**, **c** are the input and output vectors respectively [27, 29]. Let

$$\mathbf{f}(n) = \mathbf{A}^n \mathbf{b} \tag{2.2.8}$$

be a kernel group of size M. Since  $\mathbf{f}(n-1) = \mathbf{A}^{n-1}\mathbf{b} = \mathbf{A}^{-1}\mathbf{f}(n)$ , this kernel group satisfies the shift property with

$$\mathbf{R} = \mathbf{A}^{-1} \quad \text{and} \quad \mathbf{f}(0) = \mathbf{b}. \tag{2.2.9}$$

From (2.2.7) and (2.2.8) we get the linear decomposition of the mapping operator coefficients  $h_n = \mathbf{cf}(n)$ . Therefore, the time-recursive implementation of the mapping operator can be based on the kernel group  $\mathbf{f}(\cdot)$ . In our construction, the size of the kernel group M is equal to the order of the realization  $\{\mathbf{A}, \mathbf{b}, \mathbf{c}\}$ . Thus, minimizing the number of the decomposition kernels is equivalent to minimizing the order of the the partial realization of the LTI system, for which the first N Markov parameters are equal to the coefficients of our operator.  $\square$

The importance of Lemma 2.4 stems from the fact that the problem of the minimal partial realization has a well known solution [27, 29] (see for an example [27, pp.491-492]). By using this result in combination with Lemma 2.4 we can obtain a time-recursive algorithm for an arbitrary mapping operator based on the minimum number of kernels. The extended algorithm design procedure is described in the following Subsection.

# 2.2.5 On a Systematic Design II

For the time-recursive implementation of an arbitrary mapping operator  $[h_0 \ h_1 \ \cdots \ h_{N-1}]$  three steps need to be added at the beginning of the design procedure in Subsection 2.2.3:

# Design Procedure Supplement

# Input:

The mapping operator  $[h_0 \ h_1 \ \cdots \ h_{N-1}]$ .

#### Step 0.1:

Use the algorithm for the minimal order partial realization in order to compute the quantities  $\mathbf{A}$ ,  $\mathbf{b}$  and  $\mathbf{c}$  in (2.2.7) [27, 29].

#### Step 0.2:

Use the similarity transform that will yield  $\{A, b, c\}$  in the modal canonical form.

#### Step 0.3:

Calculate the close form expression for the operator coefficients.  $\Box$

The expression specified in Step 0.3 can be used as the input in the design procedure described in Subsection 2.2.3.

Note that the algorithm we refer to in Step 0.1 returns a state space description of an LTI system in the controller canonical form (see Subsection 2.1.2). By transforming this system in the modal canonical form we are able to compute the close forms of the elements in matrix  $\mathbf{A}^n$  (since this is a block diagonal matrix where the blocks are either rotation matrices or real scalars). Consequently, Step 0.3 can be carried out by simple algebraic manipulations.

#### 2.2.6 The Difference Equation Property

A fundamental property of the Markov parameters  $\{h_n = \mathbf{c}\mathbf{A}^n\mathbf{b}, \ n = 0, 1, \cdots\}$  of LTI systems dictates:

$$h_{n+M} + \alpha_M h_{n+M-1} + \dots + \alpha_1 h_n = 0,$$

where  $\alpha_p$ ,  $p = 1, 2, \dots, M$  are the constants specified in (2.1.3) [27]. Equivalently, this can be written in a difference equation format as follows:

$$h_n = \gamma_M h_{n-1} + \dots + \gamma_1 h_{n-M}, \tag{2.2.10}$$

where

$$\gamma_p = -\alpha_p, \quad p = 1, 2, \dots, M.$$

(2.2.11)

Let  $\mathbf{e}_p$  be the row vector of length M, for which the  $p^{\mathrm{th}}$  element is unity and all other elements equal zero. If vector  $\mathbf{c}$  equals  $\mathbf{e}_p$  then (2.2.7) implies that  $h_n$  is the  $p^{\mathrm{th}}$  kernel function of the kernel group  $\mathbf{f}(\cdot)$ . Suppose now that  $\mathbf{A}$  and  $\mathbf{b}$  are of the form specified in (2.1.3). Then, all kernel functions in (2.2.8) satisfy the same difference equation (2.2.10). The upcoming Lemma 2.5 states that this is true even if  $\mathbf{A}$  and  $\mathbf{b}$  do not have any special structure. Thus, it introduces the following property of a kernel group:

Difference Equation Property: A kernel group  $\mathbf{f}(\cdot) = [f_0(\cdot) \ f_1(\cdot) \ \cdots \ f_{M-1}(\cdot)]^T$ , satisfies the difference equation property (DEP) if there are scalars  $\gamma_p, p = 1, 2, \dots, M$ , independent of n, such that the kernel functions  $f_q(\cdot), q = 1, 2, \dots, M$

$0, 1, \cdots, M-1$  satisfy the following difference equation

$$f_q(n) = \gamma_1 f_q(n-1) + \dots + \gamma_M f_q(n-M)$$

$n = 1, 2, \dots, N$  (2.2.12)

with some specified initial conditions  $f_q(n), n=-1,-2,\cdots,-M$ .  $\square$

**Lemma 2.5** A kernel group satisfies DEP if and only if it satisfies SP. □

# 2.3 Design of a Time-Recursive Architecture

The proof of this Lemma is given in the Appendix.

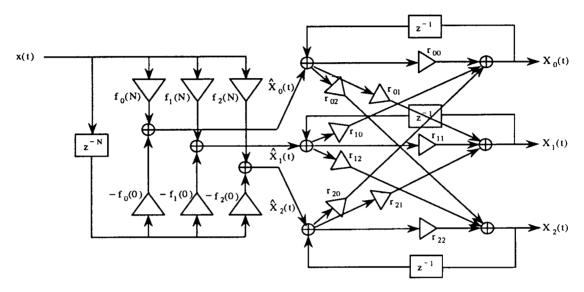

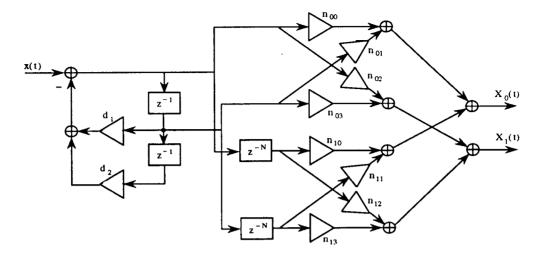

# 2.3.1 Lattice Architecture Design for Mapping Operators

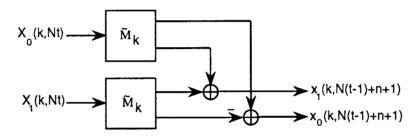

In the previous Section, we have seen how we can specify the kernel group of minimal size that is associated to a given mapping operator and how we can implement this operator by evaluating (2.2.3) and (2.2.6). The algorithm resulted by the design procedure in Subsections 2.2.3 and 2.2.5 can be realized by the lattice architecture introduced in Section 2.1 that evaluates (2.2.3), followed by a simple weighted-sum circuit that evaluates (2.2.6). The lattice architecture that implements a kernel group of size M=2 is shown in Fig. 2.1, while the one that implements a kernel group of size M=3 is depicted in Fig. 2.3. We can observe that this architecture consists of M 2-tap FIR filters and a  $M \times M$  weighted interconnection network with M feedback loops. The total cost of this structure is  $M^2 + 2M$  multipliers and  $M(M-1) + 2M = M^2 + M$  2-input adders. The weighted-sum circuit consists of M multipliers and M-1 adders. The cost of the overall implementation is given on Table 2.1.

The  $M \times M$  weighted interconnection network is characterized by the matrix R specified in (2.2.9). If we follow all five steps of the design procedure described in Subsections 2.2.3 and 2.2.5 the matrix R will be block diagonal with blocks consisted of plain rotations. Consequently, we can implement the interconnection network very efficiently, with locally interconnected rotation circuits. The latter can be realized either with CORDIC processors [23] or with distributed arithmetic techniques [52]. The cost for implementing a mapping operator with

this approach is shown on Table 2.1. Furthermore, with this setup we can exploit the fact that the absolute values of the eigenvalues of a normalized paraunitary system [54] are all equal to 1 [54, 55]. The Discrete Wavelet Transform implementation presented in Chapter 3 takes advantage of this fact to reduce the number of multipliers to be implemented.

Figure 2.3: Lattice architecture for kernel group of size M=3.

|         |                      | multipliers    | $\operatorname{adders}$ | rotations    |

|---------|----------------------|----------------|-------------------------|--------------|

| Case a. | lattice architecture | $M^2 + 3M$     | $M^2 + 3M - 1$          | -            |

|         | lattice / modal      | 2M             | [5M/2 + 1]              | M            |

|         | IIR architecture     | 3M             | 3M-1                    | -            |

| Case b. | lattice architecture | $M^2 + 2M + 1$ | $M^2 + 2M - 2$          | -            |

|         | lattice / modal      | 2M             | [5M/2 + 1]              | M/2          |

|         | IIR architecture     | 2M             | 2M                      | -            |

| Case c. | lattice architecture | $M^2 + 2M + 1$ | $M^2 + 2M - 3$          | <del>-</del> |

|         | lattice / modal      | 2M             | $\lfloor 5M/2 \rfloor$  | M/2          |

|         | IIR architecture     | 2 <i>M</i>     | 2M-1                    |              |

Table 2.1: Implementation cost of a mapping operator, based on a kernel group of size M: Case a, the operator does not satisfy the periodicity property and it is utilized by a sliding transform. Case b, the operator satisfies the periodicity property and it is utilized by a sliding transform. Case c, the operator is utilized by a block transform.

#### 2.3.2 The Periodicity Property

A class of special case architectures with important implications to the implementation of the sinusoidal data transforms will be considered. With regard to the structure depicted in Fig. 2.3, suppose that there are two constants  $D_1$  and  $D_2$  such that the relation

$$\hat{X}_{p}(t) = D_{p}\hat{X}_{0}(t), \tag{2.3.1}$$

is true for p=1,2 and  $t=1,2,\cdots$ . Then, one can verify that the 3 2-tap filters on Fig. 2.3 can be replaced by the structure shown on Fig. 2.4.a. The corresponding circuit for M=2 is given on Fig. 2.4.b.

Figure 2.4: Part of lattice architecture if the periodicity property is satisfied.

In this way, M-1 multipliers and an equal number of adders are saved. Obviously, the same trick can be used for a kernel group of arbitrary size. The resulted cost metrics are depicted on Table 1.2. In Lemma 2.6 that follows, we state a condition on the kernel functions that imply (2.3.1) and consequently the savings mentioned above can be obtained. We will see that this condition amounts to satisfaction of the following property:

**Periodicity Property:** A kernel group  $\mathbf{f}(\cdot) = [f_0(\cdot) \ f_1(\cdot) \ \cdots \ f_{M-1}(\cdot)]^T$ , satisfies the periodicity property (PP) if the following relation holds:

$$\frac{f_0(N)}{f_0(0)} = \frac{f_1(N)}{f_1(0)} = \dots = \frac{f_{M-1}(N)}{f_{M-1}(0)} = \frac{1}{S}$$

(2.3.2)

for some non-zero constant S.  $\square$

**Lemma 2.6** Given a kernel group  $\mathbf{f}(\cdot)$  relation (2.3.1) holds for  $p = 1, 2, \dots, M-1$  and  $t = 0, 1, \dots$  if  $\mathbf{f}(\cdot)$  satisfies the periodicity property.  $\square$

The proof is given in the Appendix.

The name "periodicity property" is justified by the following special case: Consider the kernel group specified by Statement 2 in Lemma 2.2, that is,

$$\begin{bmatrix} f_0(n) \\ f_1(n) \end{bmatrix} = \begin{bmatrix} c_{00}b^n + c_{01}b^{-n} \\ c_{10}b^n + c_{11}b^{-n} \end{bmatrix}, \tag{2.3.3}$$

where b is a non-zero parameter and the coefficients are free parameters, such that  $c_{00}c_{11} - c_{01}c_{10} \neq 0$ . In the Appendix we prove the following Lemma:

**Lemma 2.7** If the parameter b of the kernel group (2.3.3) is of the form  $b = e^{j\beta}$ , then (2.3.3) satisfies the periodicity property if and only if  $\beta = j\frac{k\pi}{N}$ , that is, if the kernel functions are periodic with period equal to N. Furthermore, if PP is satisfied the ratio value in (2.3.2) is equal to  $1/S = (-1)^k$ .  $\square$

An example of kernel group that satisfies PP is  $\mathbf{f}_k(n) = \left[\cos\frac{k\pi}{N}(n+\frac{1}{2})\sin\frac{k\pi}{N}(n+\frac{1}{2})\right]^T$ . This is a special case of (2.3.3) for which the values of the constants are specified in (2.2.4). We can implement the pair of DCT and DST based on this kernel group. The importance of the periodicity property will be further appreciated when we see the implications it has on the IIR architecture discussed in the following Subsections.

#### 2.3.3 IIR Architecture Based on the Shift Property

The lattice architecture we have seen in Subsection 2.3.1 constitutes a direct translation of (2.2.3) into an architectural implementation. If a transfer function approach is adopted instead, we obtain an IIR filter structure implementation for (2.1.1) [34]. In this Subsection, we show how we can specify the IIR implementation of a kernel group based on the shift property, while the IIR architecture design based on the difference equation property is the subject of the following Subsection. The IIR architecture often involves less implementation

cost in comparison to the lattice one, especially if the associated kernel group exhibits the periodicity property we have seen in the previous Subsection.

**Lemma 2.8** Let  $f_p(\cdot)$  be a kernel function in the kernel group  $\mathbf{f}(\cdot) = [f_0(\cdot) \ f_1(\cdot) \ \cdots \ f_{M-1}(\cdot)]^T$  of size M. If  $\mathbf{f}(\cdot)$  satisfies SP, the kernel function  $f_p(\cdot)$  can be implemented by an IIR filter with transfer function  $H_p(z)$

$$H_p(z) = \frac{b_p^0(z)}{a(z)} - z^{-N} \frac{b_p^1(z)}{a(z)}, \quad p = 0, 1, \dots, M - 1, \tag{2.3.4}$$

where a(z) is a polynomial in  $z^{-1}$  of degree M and  $b_p^i$ , i=0,1 are polynomials in  $z^{-1}$  of degree M-1, defined as follows:  $a(z)=|\mathbf{A}(z)|$ ,  $b_p^i(z)=\left|\mathbf{B}_p^i(z)\right|$ , i=0,1,

$$a(z) = \begin{bmatrix} -1 + r_{00}z^{-1} & r_{01}z^{-1} & \cdots & r_{0,P-1}z^{-1} \\ r_{10}z^{-1} & -1 + r_{11}z^{-1} & \cdots & r_{1,P-1}z^{-1} \\ \vdots & \vdots & \ddots & \vdots \\ r_{P-1,0}z^{-1} & r_{P-1,1}z^{-1} & \cdots & -1 + r_{P-1,P-1}z^{-1} \end{bmatrix}.$$

(2.3.5)

$\mathbf{B}_{p}^{i}(z)$  is an  $M \times M$  matrix that is formed by substituting the  $p^{\text{th}}$  column of  $\mathbf{A}(z)$  with  $\left[s_{0}^{i} \ s_{1}^{i} \ \cdots \ s_{M-1}^{i}\right]^{T} \ i=0,1$ , where

$$s_p^0 = -\sum_{q=0}^{M-1} r_{pq} f_q(0), \quad s_p^1 = -\sum_{q=0}^{M-1} r_{pq} f_q(N), \quad p = 0, 1, \dots, M-1.$$

Note that |X| denotes the determinant of the matrix X.  $\Box$

The proof is given in the Appendix.

As a direct consequence of this Lemma we have:

Corollary 2.2 Let  $\mathbf{f}(\cdot) = [f_0(\cdot) \ f_1(\cdot) \ \cdots \ f_{M-1}(\cdot)]^T$  be a kernel group of size M that satisfies PP. Then, the transfer function  $H_p(z)$  of the linear system that models (2.2.3) is:

$$H_p(z) = \left(S - z^{-N}\right) \frac{b_p^1(z)}{a(z)}, \quad p = 0, 1, \dots, M - 1,$$

(2.3.6)

where a(z) and  $b_p^1(z)$  are specified in Lemma 2.8 and S is the constant specified in (2.3.2).  $\square$

For the sake of clarity, we will consider the special case of a kernel group of size M=2 in detail. Let  $H_p(z)$  be the transfer function of the linear system that models the mapping operators

$$[f_p(0) f_p(1) \cdots f_p(N-1)],$$

for p = 0, 1. From (2.3.5), for M = 2 we get:

$$a(z) = \begin{vmatrix} -1 + r_{00}z^{-1} & r_{01}z^{-1} \\ r_{10}z^{-1} & -1 + r_{11}z^{-1} \end{vmatrix}.$$

Furthermore, we have

$$b_0^i(z) = \begin{vmatrix} s_0^i & r_{01}z^{-1} \\ s_1^i & -1 + r_{11}z^{-1} \end{vmatrix}, \quad b_1^i(z) = \begin{vmatrix} -1 + r_{00}z^{-1} & s_0^i \\ r_{10}z^{-1} & s_1^i \end{vmatrix},$$

where

$$s_p^0 = -r_{p0}f_0(0) - r_{p1}f_1(0)$$

and  $s_p^1 = -r_{p0}f_0(N) - r_{p1}f_1(N)$ ,  $p = 0, 1$ .

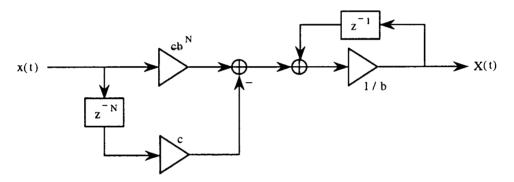

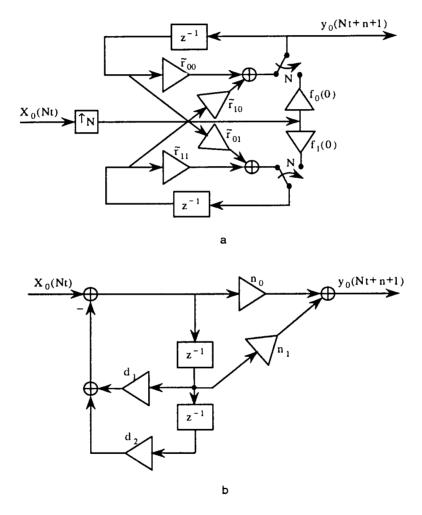

The architectural implementation resulted from (2.3.4) is shown in Fig. 2.5, while for the case where the periodicity property is satisfied, the architecture associated to (2.3.6) is depicted on Fig. 2.6. We observe that the IIR architecture consists of a feedback structure with M=2 delay elements. The parameters  $d_i$ , i=1,2 and  $n_{ij}$ , i=0,1,j=0,1,2,3 are given by the following expressions:

$$d_{1} = -r_{00} - r_{11} n_{00} = f_{0}(N)r_{00} + f_{1}(N)r_{01} n_{10} = f_{0}(0)r_{00} + f_{1}(0)r_{01}$$

$$d_{2} = r_{00}r_{11} - r_{01}r_{10} n_{01} = -f_{0}(N)d_{2} n_{11} = -f_{0}(0)d_{2}$$

$$n_{02} = f_{0}(N)r_{10} + f_{1}(N)r_{11} n_{12} = f_{0}(0)r_{10} + f_{1}(0)r_{11}$$

$$n_{03} = -f_{1}(N)d_{2} n_{13} = -f_{1}(0)d_{2} .$$

$$(2.3.7)$$

Figure 2.5: IIR architecture for M=2.

Figure 2.6: IIR architecture for M=2 if the periodicity property is satisfied.

Figure 2.7: IIR architecture for M=3 if the periodicity property is satisfied.

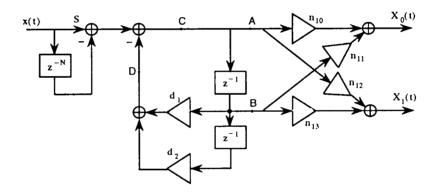

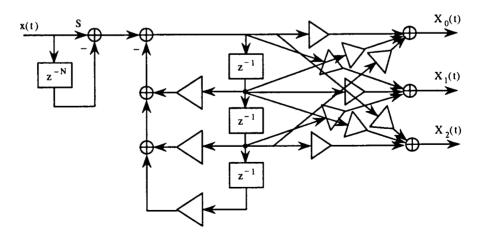

### 2.3.4 IIR Architecture Based on the Difference Equation Property

An alternative approach to the problem of designing the IIR architecture is based on the defining equation of  $X_p(t)$  (2.2.2) and the difference equation property of the kernel group specified in Lemma 2.5. In more concrete terms, we can compute the  $\mathcal{Z}$  transform of a kernel function  $f_p(n)$  based on the difference equation (2.2.12) and then calculate the transfer function of the system specified by (2.2.2). The following lemmas describe how we can obtain the desired transfer function if we are specified the difference equation parameters. The special case of a difference equation of order M=2 is first considered, the reason being both its importance for a number of practical applications [34] and its simplicity.

**Lemma 2.9** Let the kernel function  $f_p(\cdot)$  satisfy the second order difference equation

$$f_p(n) = \gamma_1 f_p(n-1) + \gamma_2 f_p(n-2), \quad n = 1, 2, \dots, N.$$

(2.3.8)

The transfer function  $H_p(z)$  of the system specified in (2.2.2) is

$$H_p(z) = \frac{f_p(N-1) + \frac{1}{\gamma_2} f_p(N) z^{-1}}{1 - \frac{\gamma_1}{\gamma_2} z^{-1} - \frac{1}{\gamma_2} z^{-2}} - z^{-N} \frac{f_p(-1) + \frac{1}{\gamma_2} f_p(0) z^{-1}}{1 - \frac{\gamma_1}{\gamma_2} z^{-1} - \frac{1}{\gamma_2} z^{-2}}. \quad \Box$$

(2.3.9)

The proof of this Lemma was originally given in [34]. In Appendix, we present a proof with more elaborate formalization that suggests the generalization considered in Lemma 2.10.

The parameter values of the associated IIR architecture in Fig. 2.5 is a direct outcome of Lemma 2.9:

$$d_{1} = -\gamma_{1}/\gamma_{2} \quad n_{00} = f_{0}(N-1) \quad n_{10} = f_{0}(-1)$$

$$d_{2} = -1/\gamma_{2} \quad n_{01} = f_{0}(N)/\gamma_{2} \quad n_{11} = f_{0}(0)/\gamma_{2}$$

$$n_{02} = f_{1}(N-1) \quad n_{12} = f_{1}(-1)$$

$$n_{03} = f_{1}(N)/\gamma_{2} \quad n_{13} = -f_{1}(0)/\gamma_{2}$$

$$(2.3.10)$$

The generalization of Lemma 2.9 for arbitrary values of the order M of the difference equation follows:

**Lemma 2.10** Let the kernel function  $f_p(\cdot)$  satisfy the  $M^{\text{th}}$  order difference equation (2.2.12). Then, the transfer function  $H_p(z)$  of the system specified in (2.2.2) is given by the expression in (2.3.4), where

$$a(z) = 1 + \sum_{n=0}^{M-1} \frac{\gamma_{M-n}}{\gamma_M} z^{-n} - \frac{1}{\gamma_M} z^{-M}$$

$$b_p^0(z) = \sum_{n=0}^{M-1} \left[ \frac{1}{\gamma_n} \sum_{q=M-n}^{M} \gamma_q f_p(N+M-n-q-1) \right] z^{-n} \qquad (2.3.11)$$

$$b_p^1(z) = \sum_{n=0}^{M-1} \left[ \frac{1}{\gamma_n} \sum_{q=M-n}^{M} \gamma_q f_p(M-n-q-1) \right] z^{-n}. \quad \Box$$

Lemma 2.10 gives a means for computing the IIR parameter values that is considerably easier from the alternative way of carrying out the algebraic computations involved in (2.3.4). Finally, as a direct consequence of Lemma 2.10 we have:

Corollary 2.3 Let the kernel function  $f_p(\cdot)$  satisfy:

- 1. The  $M^{ ext{th}}$  order difference equation (2.2.12).

- 2. The condition

$$\frac{f_p(N)}{f_p(0)} = \frac{f_p(N-1)}{f_p(-1)} = \dots = \frac{f_p(N-M+1)}{f_p(-M+1)} = S,$$

(2.3.12)

for some constant S.

Then, the transfer function  $H_p(z)$  of the system specified in (2.2.2) is given by (2.3.6), where a(z) and  $b_p^1(z)$  are specified in (2.3.11) and S in (2.3.12).  $\square$

We may observe that (2.3.12) has the same effect on the IIR architecture with (2.3.2), the defining equation of the periodicity property for a kernel group. This fact suggests the following extension of the definition of the periodicity property: