# THESIS REPORT

Ph.D.

**Algorithm-Based Low-Power Digital Signal Processing System Designs**

by A-Y. Wu

Advisor: K.J.R. Liu

Ph.D. 95-6

Sponsored by the National Science Foundation Engineering Research Center Program, the University of Maryland, Harvard University, and Industry

#### Algorithm-Based Low-Power Digital Signal Processing System Designs

by

An-Yeu (Andy) Wu

Dissertation submitted to the Faculty of the Graduate School of The University of Maryland in partial fulfillment of the requirements for the degree of Doctor of Philosophy

1995

#### Advisory Committee:

Professor K. J. Ray Liu, Chairman/Advisor

Professor Rama Chellappa Professor Kazuo Nakajima

Professor Dianne O'Leary

Professor Steve Tretter

ABSTRACT

Title of Dissertation:

Algorithm-Based Low-Power Digital

Signal Processing System Designs

An-Yeu (Andy) Wu, Doctor of Philosophy, 1995

Dissertation directed by: Professor K. J. Ray Liu

Department of Electrical Engineering

In most low-power VLSI designs, the supply voltage is usually reduced to lower the total power consumption. However, the device speed will be degraded as the supply

voltage goes down. In order to meet the low-power/high-throughput constraint, the key

issue is to "compensate" the increased delay so that the device can be operated at the

slowest possible speed without affecting the system throughput rate.

In this dissertation, new algorithmic-level techniques for compensating the increased

delays based on the multirate approach are proposed. Given the digital signal processing

(DSP) problems, we apply the multirate approach to reformulate the algorithms so that

the desired outputs can be obtained from the decimated input sequences. Since the data

rate in the resulting multirate architectures is M-times slower than the original data

rate while maintaining the same throughput rate, the speed penalty caused by the low

supply voltage is compensated at the algorithmic/architectural level.

This new low-power design technique is applied to several important DSP applica-

tions. The first one is a design methodology for the low-power design of FIR/IIR systems.

By following the proposed design procedures, users can convert a speed-demanding sys-

tem function into its equivalent multirate transfer function. This methodology provides a

systematic way for VLSI designers to design low-power/high-speed filtering architectures

at the algorithmic/architectural level.

The multirate approach is also applied to the low-power transform coding architecture design. The resulting time-recursive multirate transform architectures inherit all advantages of the existing time-recursive transform architectures such as local communication, regularity, modularity, and linear hardware complexity, but the speed for updating the transform coefficients becomes M-times slower.

The last application is a programmable video co-processor system architecture that is capable of performing FIR/IIR filtering, subband filtering, discrete orthogonal transforms (DT) and adaptive filtering for the host processor in video applications. The system can be easily reconfigurated to perform multirate FIR/IIR/DT operations. Hence, we can either double the processing speed on-the-fly based on the same processing elements, or apply this feature to the low-power implementation of this co-processor.

The methodology and the applications presented in this dissertation constitute a design framework for achieving low-power consumption at the algorithmic/architectural level for DSP applications.

© Copyright by An-Yeu (Andy) Wu 1995

#### Dedication

TO MY PARENTS, CHANG-TIEN WU AND LING-BO HSU.

To my dear wife, Ju-Hsing Li

for her patience, support, and love during writing of this work.

#### Acknowledgements

I would like to express my gratitude to my advisor, Dr. Ray Liu for his guidance, encouragement, and support throughout the course of my graduate studies. His insightful advice always inspired me when I faced difficulties in research and personal life. My time with him has been a rewarding unforgetable experience.

I am grateful to those professors who have taught me in the graduate courses. Special thanks go to Dr. Ahmet Y. Oruc, Dr. Linda Milor, Dr. Rama Chellappa, and Dr. Kazuo Nakajima. They helped me to build most of the necessary background for my research projects.

I would also like to thank my friends in the Digital Signal Processing Laboratory for their assistance and numerous interesting discussions, especially, Dr. Ye Li, Ut-Va Koc, Hong-Yi Wang, Vishnuuss Srinivasan, Arun Raghupathy, and Shang-Chieh Liu. Also, I am would like to acknowledge Zhongying Zhang of VLSI Design Automation Laboratory for providing his low-power chip designs.

Finally, I thank my family and friends for their constant love and support.

### Table of Contents

| Se | ction | <u>n</u> <u>P</u>                                                    | age  |

|----|-------|----------------------------------------------------------------------|------|

| Li | st of | Tables                                                               | viii |

| Li | st of | Figures                                                              | x    |

| 1  | Intr  | roduction                                                            | 1    |

|    | 1.1   | Low-Power VLSI Design Approaches                                     | 2    |

|    | 1.2   | Algorithmic/Architectural-level Low-Power Design Using the Multirate |      |

|    |       | Approach                                                             | 6    |

|    | 1.3   | Main Contributions                                                   | 8    |

|    | 1.4   | Thesis Organization                                                  | 11   |

| 2  | Des   | sign Methodology for Multirate FIR/IIR Systems                       | 13   |

|    | 2.1   | Basic Multirate Operations                                           | 14   |

|    | 2.2   | Multirate Design Methodology                                         | 18   |

|    |       | 2.2.1 Low-Power Multirate IIR System                                 | 24   |

|    | 2.3   | Diagonalization of the Pseudocirculant Matrix                        | 25   |

|    | 2.4   | Power Estimation for the Multirate FIR Architecture                  | 27   |

|    | 2.5   | Design of the Low-Power QMF Filter                                   | 28   |

|    |       | 2.5.1 Choice of QMF Coefficients                                     | 29   |

|    |       | 2.5.2 Choice of System Wordlength                                    | 32   |

|   |            | 2.5.3                                            | Chip Design and Simulation Results                                                                                                                                                                                                                                                | 32                                                 |

|---|------------|--------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|----------------------------------------------------|

| 3 | Μι         | ıltirate                                         | e DCT/IDCT Architectures                                                                                                                                                                                                                                                          | 38                                                 |

|   | 3.1        | The C                                            | hebyshev Polynomial Approach                                                                                                                                                                                                                                                      | 39                                                 |

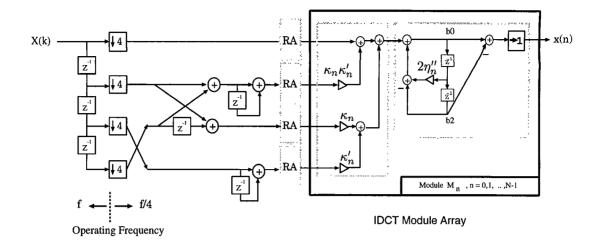

|   |            | 3.1.1                                            | Chebyshev IDCT Architecture                                                                                                                                                                                                                                                       | 40                                                 |

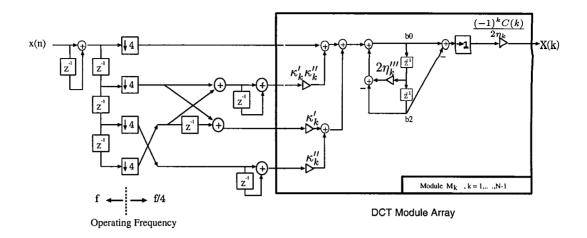

|   |            | 3.1.2                                            | Chebyshev DCT Architecture                                                                                                                                                                                                                                                        | 42                                                 |

|   |            | 3.1.3                                            | Low-Power Design for the DCT/IDCT                                                                                                                                                                                                                                                 | 43                                                 |

|   | 3.2        | The P                                            | olyphase Decomposition Approach                                                                                                                                                                                                                                                   | 49                                                 |

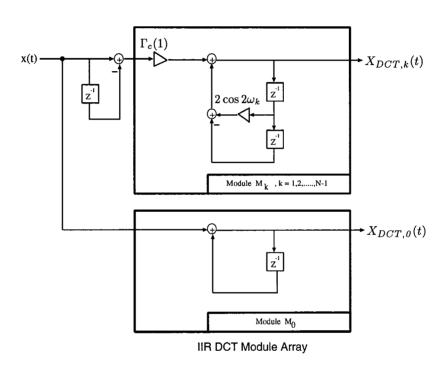

|   |            | 3.2.1                                            | The IIR DCT Algorithm                                                                                                                                                                                                                                                             | 50                                                 |

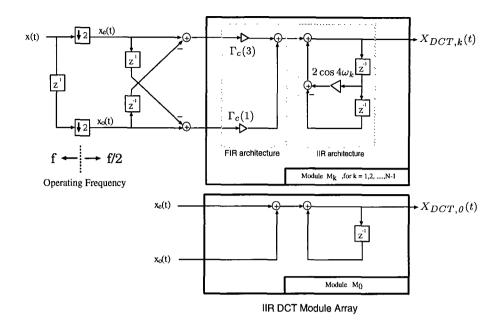

|   |            | 3.2.2                                            | Low-Power Design of the IIR DCT                                                                                                                                                                                                                                                   | 50                                                 |

|   |            | 3.2.3                                            | Low-Power Design of the IIR IDCT                                                                                                                                                                                                                                                  | 55                                                 |

|   |            | 3.2.4                                            | Polyphase Representation                                                                                                                                                                                                                                                          | 57                                                 |

|   | 3.3        | Comp                                             | arisons of Architectures                                                                                                                                                                                                                                                          | 58                                                 |

|   |            |                                                  |                                                                                                                                                                                                                                                                                   |                                                    |

| 4 | Lo         | garith                                           | mic Low-power Design and Unified Low-Power Transform                                                                                                                                                                                                                              |                                                    |

| 4 |            |                                                  | mic Low-power Design and Unified Low-Power Transform                                                                                                                                                                                                                              | 62                                                 |

| 4 |            | ding A                                           | •                                                                                                                                                                                                                                                                                 |                                                    |

| 4 | Cod        | ding A                                           | rchitecture                                                                                                                                                                                                                                                                       | 62                                                 |

| 4 | Cod        | ling A                                           | rchitecture Cower Architecture of Logarithmic Complexity                                                                                                                                                                                                                          | <b>62</b> 63                                       |

| 4 | Cod        | Low-F<br>4.1.1<br>4.1.2                          | control complexity                                                                                                                                                                                                                                                                | <b>62</b> 63 64                                    |

| 4 | 4.1        | Low-F<br>4.1.1<br>4.1.2                          | consumption                                                                                                                                                                                                                                                                       | 62<br>63<br>64<br>65<br>68                         |

| 4 | 4.1        | Low-F<br>4.1.1<br>4.1.2<br>Low-F                 | Cower Architecture of Logarithmic Complexity                                                                                                                                                                                                                                      | 62<br>63<br>64<br>65<br>68                         |

| 4 | 4.1        | Low-F<br>4.1.1<br>4.1.2<br>Low-F<br>4.2.1        | Cower Architecture of Logarithmic Complexity                                                                                                                                                                                                                                      | 62<br>63<br>64<br>65<br>68                         |

| 4 | 4.1        | Low-F 4.1.1 4.1.2 Low-F 4.2.1 4.2.2 4.2.3        | Cower Architecture of Logarithmic Complexity  Low-Power DCT Architecture of Logarithmic Complexity  Power Consumption  Cower MLT and ELT Architectures  The IIR MLT Algorithm  Low-Power Design of the MLT                                                                        | 62<br>63<br>64<br>65<br>68<br>68                   |

| 4 | 4.1<br>4.2 | Low-F 4.1.1 4.1.2 Low-F 4.2.1 4.2.2 4.2.3 Unifie | Cower Architecture of Logarithmic Complexity  Low-Power DCT Architecture of Logarithmic Complexity  Power Consumption  Cower MLT and ELT Architectures  The IIR MLT Algorithm  Low-Power Design of the MLT  Low-Power Design of the ELT                                           | 62<br>63<br>64<br>65<br>68<br>68<br>69<br>72       |

|   | 4.1<br>4.2 | Low-F 4.1.1 4.1.2 Low-F 4.2.1 4.2.2 4.2.3 Unifie | Cower Architecture of Logarithmic Complexity  Low-Power DCT Architecture of Logarithmic Complexity  Power Consumption  Cower MLT and ELT Architectures  The IIR MLT Algorithm  Low-Power Design of the MLT  Low-Power Design of the ELT  d Low-Power Transform Coding Archiecture | 62<br>63<br>64<br>65<br>68<br>68<br>69<br>72<br>73 |

|                | 5.2.1                                  | Rounding Errors                                                                                                                                                                | 79                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|----------------|----------------------------------------|--------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|-----------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------------|

|                | 5.2.2                                  | Dynamic Range                                                                                                                                                                  | 81                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                | 5.2.3                                  | Optimal Wordlength Assignment                                                                                                                                                  | 83                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.3            | IIR D                                  | CT Using Direct Form II Structure                                                                                                                                              | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.4            | Analy                                  | ysis for the Low-Power IIR DCT with $M=2$                                                                                                                                      | 85                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| 5.5            | Simul                                  | lation Results                                                                                                                                                                 | 89                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

| $\mathbf{Vid}$ | eo Co-                                 | Processor Design                                                                                                                                                               | 92                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

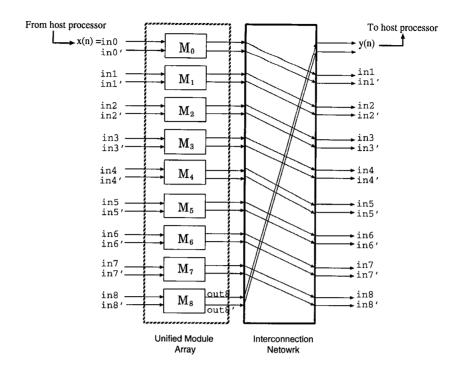

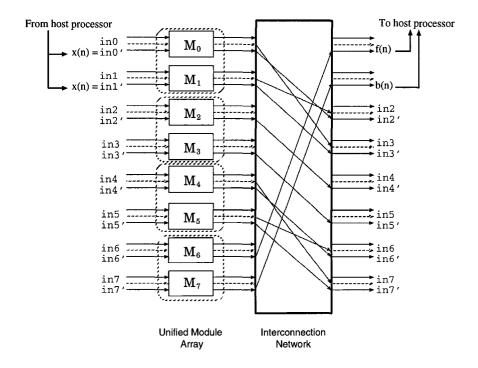

| 6.1            | Video                                  | Co-processor Design for the FIR/QMF/IIR/DT                                                                                                                                     | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                | 6.1.1                                  | Basic Module in FIR                                                                                                                                                            | 94                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                | 6.1.2                                  | Basic Module in QMF                                                                                                                                                            | 97                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                | 6.1.3                                  | Basic Module in IIR                                                                                                                                                            | 99                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                |

|                | 6.1.4                                  | Basic Module in Discrete Transforms                                                                                                                                            | 103                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                | 6.1.5                                  | Unified Module Design                                                                                                                                                          | 104                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

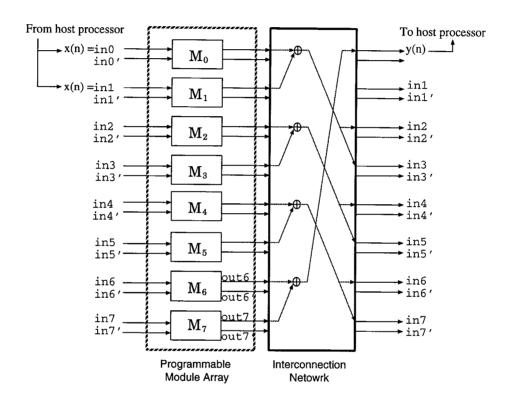

|                | 6.1.6                                  | Video Co-processor Design                                                                                                                                                      | 106                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                | 6.1.7                                  | Design Examples                                                                                                                                                                | 111                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6.2            | Speed                                  | -Up of the Video Co-processor Architecture                                                                                                                                     | 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

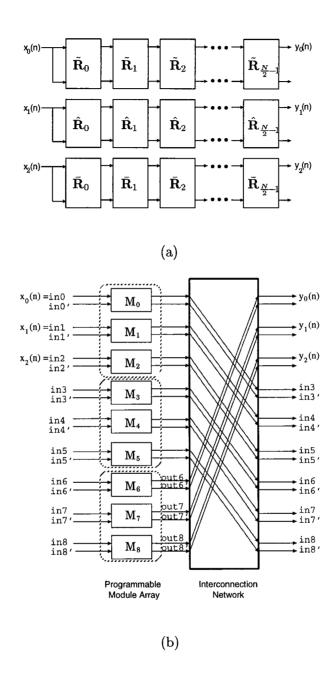

|                | 6.2.1                                  | Mapping of the Multirate FIR Architecture                                                                                                                                      | 113                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

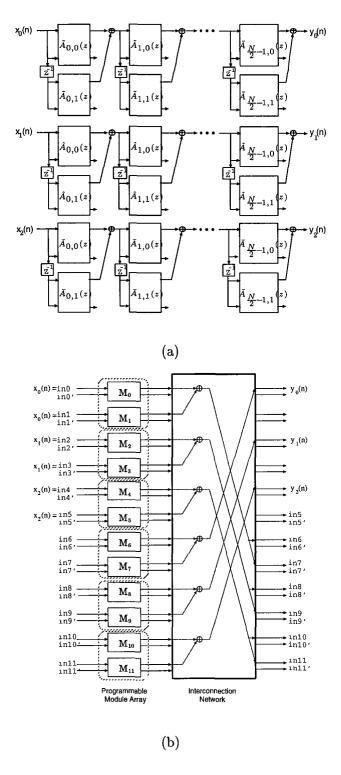

|                | 6.2.2                                  | Mapping of the Multirate IIR Architecture                                                                                                                                      | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                | 6.2.3                                  | Multirate Discrete Transform Architecture                                                                                                                                      | 117                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                | 6.2.4                                  | Application to Low-Power Design                                                                                                                                                | 120                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                | 6.2.5                                  | Design Examples Using Multirate Operations                                                                                                                                     | 122                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6.3            | Incorp                                 | poration of the QRD-LSL Adaptive Filtering                                                                                                                                     | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                | 6.3.1                                  | CORDIC Operation and QRD-LSL Architecture                                                                                                                                      | 123                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                | 6.3.2                                  | Mapping QRD-LSL to the Programmable Video Co-processor                                                                                                                         | 125                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| 6.4            | Perfor                                 | mance and Comparison                                                                                                                                                           | 129                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

| Con            | clusio                                 | ns and Future Research                                                                                                                                                         | 131                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                                               |

|                | 5.4<br>5.5<br><b>Vid</b><br>6.1<br>6.2 | 5.2.3 5.3 IIR D 5.4 Analy 5.5 Simular  Video Co- 6.1 Video 6.1.1 6.1.2 6.1.3 6.1.4 6.1.5 6.1.6 6.1.7 6.2 Speed 6.2.1 6.2.2 6.2.3 6.2.4 6.2.5 6.3 Incorp 6.3.1 6.3.2 6.4 Perfor | 5.2.3 Optimal Wordlength Assignment  5.3 IIR DCT Using Direct Form II Structure  5.4 Analysis for the Low-Power IIR DCT with M = 2  5.5 Simulation Results  Video Co-Processor Design  6.1 Video Co-processor Design for the FIR/QMF/IIR/DT  6.1.1 Basic Module in FIR  6.1.2 Basic Module in QMF  6.1.3 Basic Module in IIR  6.1.4 Basic Module in Discrete Transforms  6.1.5 Unified Module Design  6.1.6 Video Co-processor Design  6.1.7 Design Examples  6.2 Speed-Up of the Video Co-processor Architecture  6.2.1 Mapping of the Multirate FIR Architecture  6.2.2 Mapping of the Multirate IIR Architecture  6.2.3 Multirate Discrete Transform Architecture  6.2.4 Application to Low-Power Design  6.2.5 Design Examples Using Multirate Operations  6.3 Incorporation of the QRD-LSL Adaptive Filtering  6.3.1 CORDIC Operation and QRD-LSL Architecture  6.3.2 Mapping QRD-LSL to the Programmable Video Co-processor |

References 142

### List of Tables

| Numbe | <u>er</u> <u> </u>                                                                 | Page |

|-------|------------------------------------------------------------------------------------|------|

| 2.1   | PSNR results for different QMF's                                                   | 31   |

| 3.1   | Comparison of hardware cost for the DCT and IDCT architectures with                |      |

|       | their low-power designs in terms of 2-input multipliers and 2-input adders.        | 59   |

| 3.2   | Comparison of different DCT architectures, where $f_s$ denotes the data            |      |

|       | sample rate, $M$ denotes the programmable downsampling factor, and $N$             |      |

|       | is the block size.                                                                 | 61   |

| 4.1   | Comparison of hardware cost and power consumption of the logarithmic               |      |

|       | low-power DCT architecture with other approaches                                   | 67   |

| 4.2   | Comparison of hardware cost for the MLT and ELT with their low-power               |      |

|       | designs in terms of 2-input multipliers and 2-input adders                         | 72   |

| 4.3   | Parameter settings for the unified low-power IIR transformation architec-          |      |

|       | ture, where $Re\{X_{DFT,k}(t)\}$ and $Im\{X_{DFT,k}(t)\}$ denote the the real part |      |

|       | and the imaginary part of the DFT, respectively.                                   | 75   |

| 5.1   | Optimal wordlength assignment under the constraint $SNR = 40dB$ , where            |      |

|       | $B_A$ is the average wordlength. (a) Normal IIR DCT. (b) Low-power DCT             |      |

|       | with $M=2$                                                                         | 84   |

| 6.1 | Setting for the programmable module, where $N_{\text{max}}$ is the maximum order |

|-----|----------------------------------------------------------------------------------|

|     | (or block size in DT) that can be realized by a $P$ -module array, and switch    |

|     | $s_6$ is only used in the QRD-LSL operation                                      |

| 6.2 | Switch settings for the interconnection network, where $N$ denotes the           |

|     | order of the FIR/QMF/IIR/QRD-LSL or the block size of the DT 110 $$              |

| 6.3 | Settings for the (a) FIR filter, (b) QMF filter, (c) IIR (ARMA) filter, and      |

|     | (d) 8-point DCT                                                                  |

| 6.4 | Settings for the (a) FIR filter, (b) IIR (ARMA) filter, and (c) 8-point          |

|     | DCT under multirate operation                                                    |

## List of Figures

| Numbe | <u>Pa</u>                                                                      | ıge |

|-------|--------------------------------------------------------------------------------|-----|

| 1.1   | (a) Original SIPO DCT circuit. (b) Low-power DCT circuit using the             |     |

|       | multirate approach                                                             | 8   |

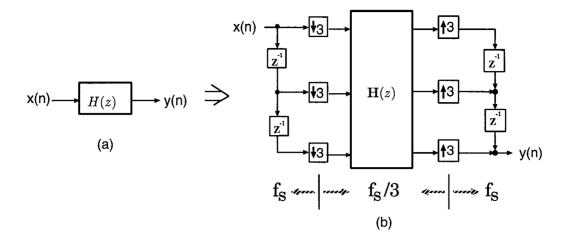

| 2.1   | (a) An LTI FIR/IIR system. (b) Its equivalent multirate implementation.        | 14  |

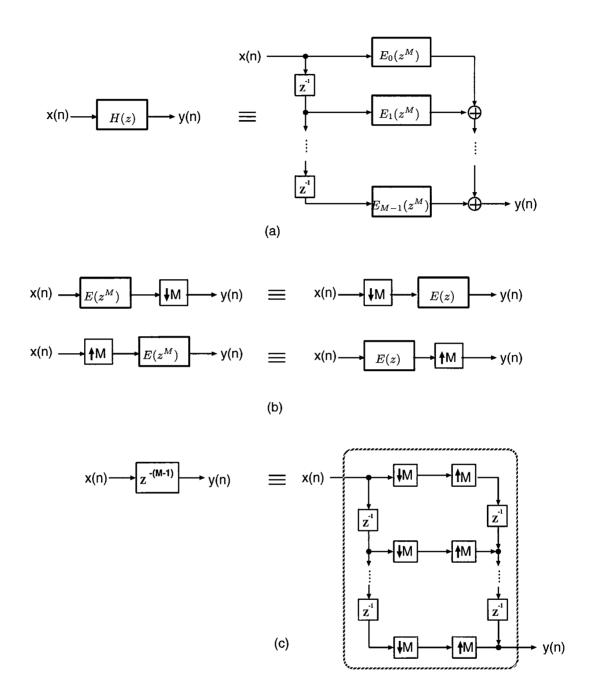

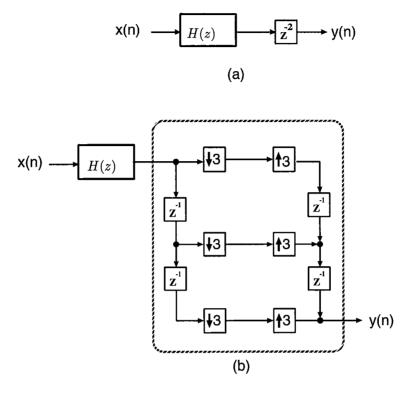

| 2.2   | Basic multirate operations: (a) Polyphase decompositon. (b) Noble iden-        |     |

|       | tities. (c) Equivalent multirate implementation of an $(M-1)$ delay element.   | 16  |

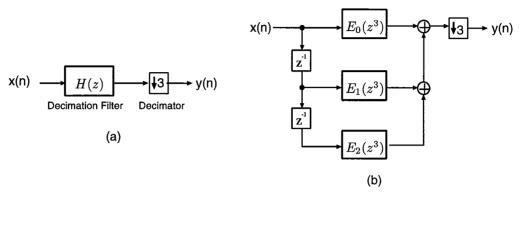

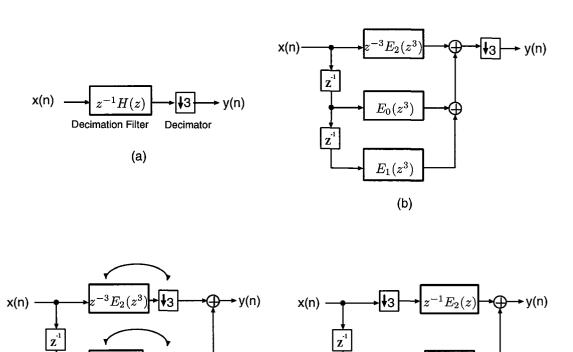

| 2.3   | Derivation of the polyphase implementation of the decimation circuit,          |     |

|       | where $f_s$ denotes the data sample rate. (a) The original decimation circuit. |     |

|       | (b) Representing the decimation filter using Fig. 2.2(a). (c) Applying the     |     |

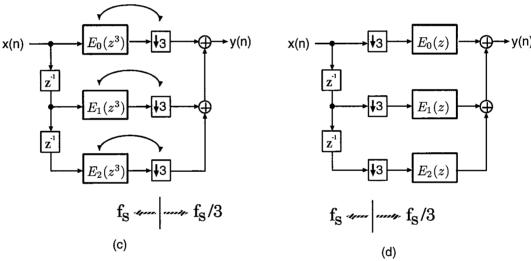

|       | noble indentity. (d) The resulting polyphase implementation                    | 17  |

| 2.4   | Derivation of the polyphase implementation of the decimation circuit with      |     |

|       | transfer function $z^{-1}H(z)$                                                 | 19  |

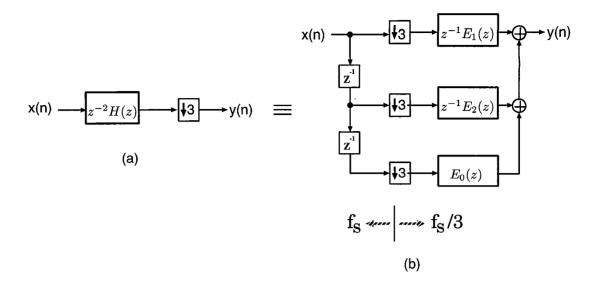

| 2.5   | The decimation circuit with transfer function $z^{-2}H(z)$                     | 20  |

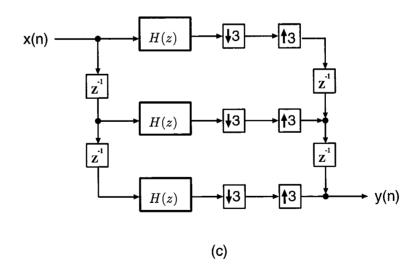

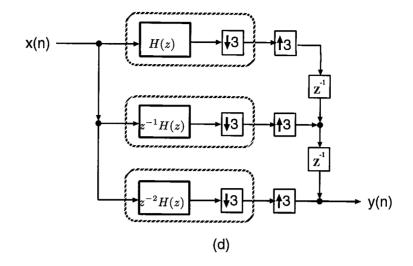

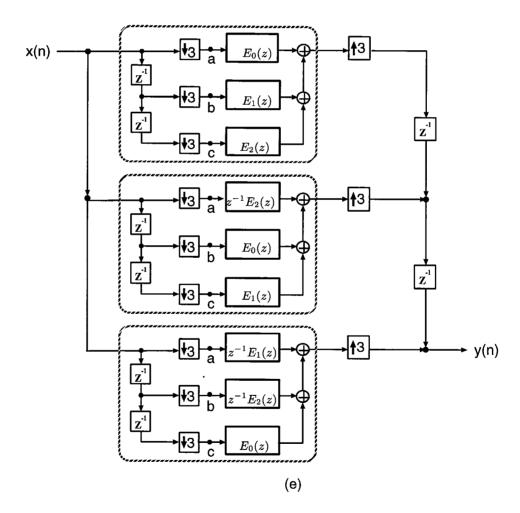

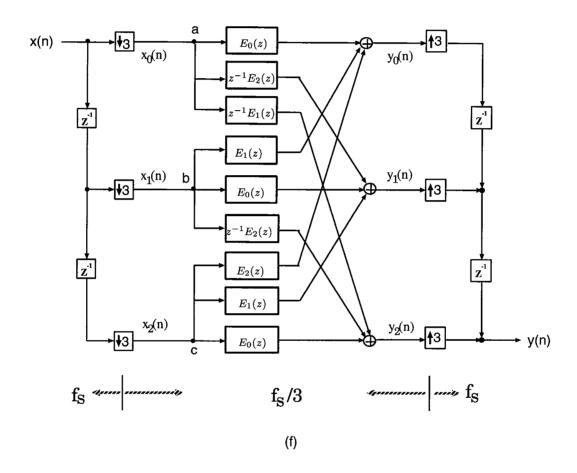

| 2.6   | Step-by-step derivation of the multirate LTI system                            | 21  |

| 2.6   | (cont.)                                                                        | 22  |

| 2.6   | (cont.)                                                                        | 23  |

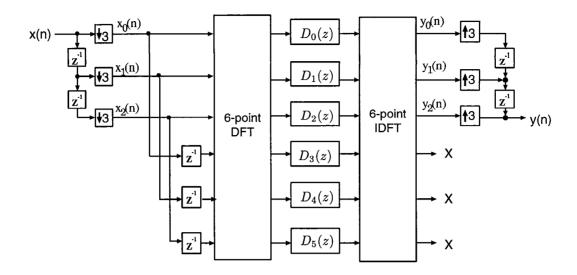

| 2.7   | Diagonalization of the pseudocirculant matrix using the FFT approach           | 26  |

| 2.8   | Multirate FIR architecture with $M=2.$                                         | 27  |

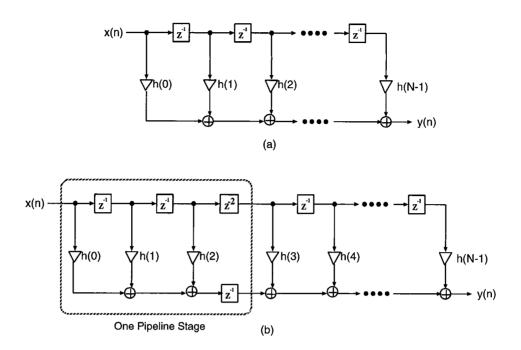

| 2.9   | (a) FIR structure. (b) FIR structure with pipelined design                     | 29  |

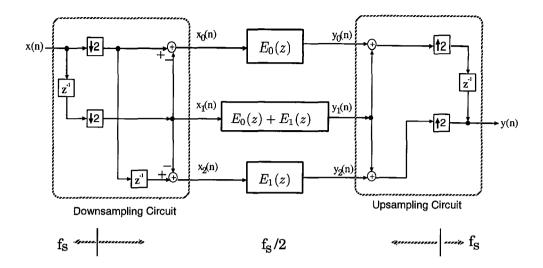

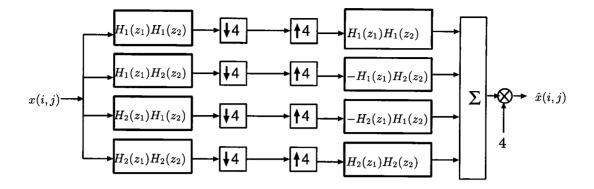

| 2.10 | The four-band 2-D QMF bank                                                                | 30 |

|------|-------------------------------------------------------------------------------------------|----|

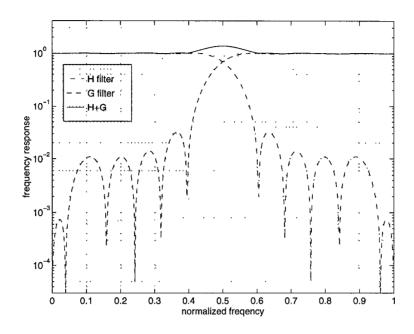

| 2.11 | Frequency response of the modified QMF filter using power-of-two coeffi-                  |    |

|      | cients                                                                                    | 31 |

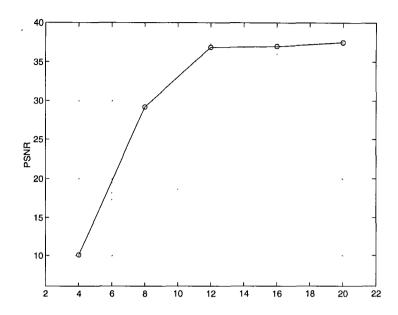

| 2.12 | PSNR results for the modified QMF as a function of system wordlength $B.$                 | 32 |

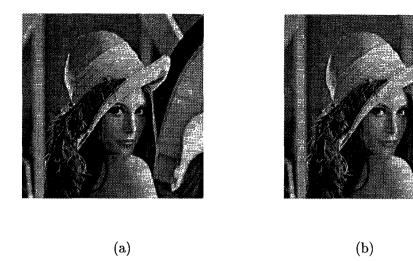

| 2.13 | (a) The original LENA image. (b) The output image of the subband cod-                     |    |

|      | ing structure based on the modified power-of-two QMF with wordlength                      |    |

|      | B = 12  (PSNR=36.9 dB)                                                                    | 33 |

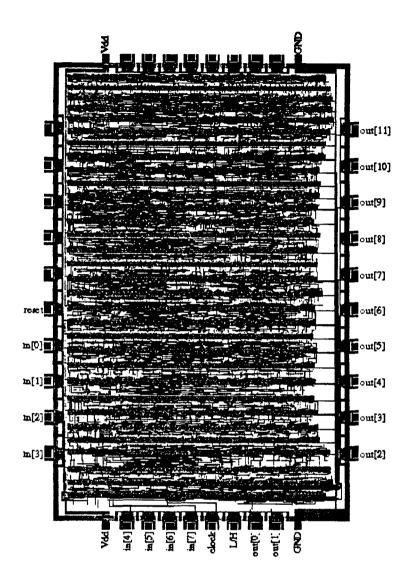

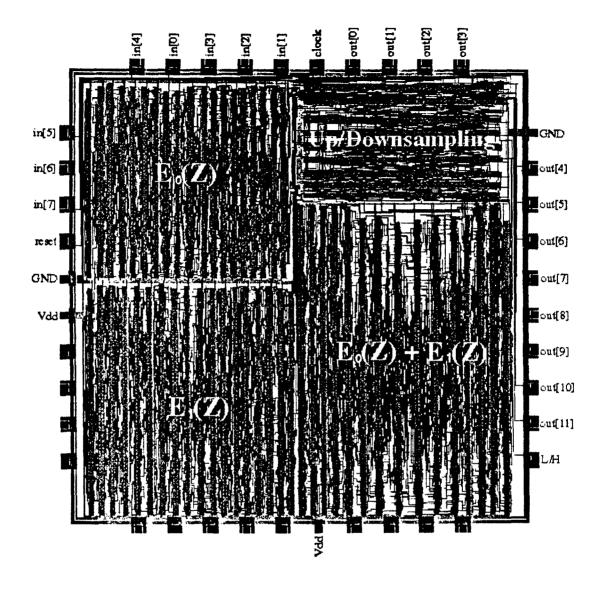

| 2.14 | Final layout of the normal QMF filter. The chip dimension is $4400 \times 6600 \lambda^2$ |    |

|      | (courtesy of Zhongying Zhang, VLSI Design Automation Labortory, Elec-                     |    |

|      | trical Engineering Department, University of Maryland at College Park).                   | 34 |

| 2.15 | Final layout of the multirate QMF filter. The chip dimension is 6500 $\times$             |    |

|      | $6600\lambda^2$ (courtesy of Zhongying Zhang, VLSI Design Automation Labor-               |    |

|      | tory, Electrical Engineering Department, University of Maryland at Col-                   |    |

|      | lege Park)                                                                                | 35 |

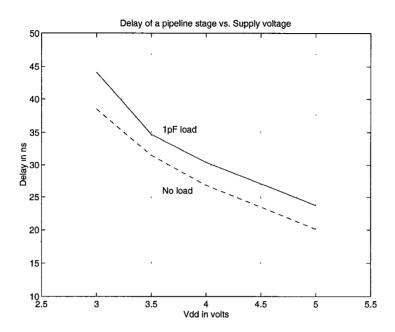

| 2.16 | Timing analysis of one pipelined stage in the FIR design                                  | 36 |

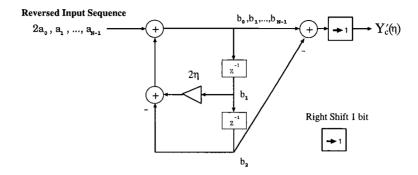

| 3.1  | Recursive architecture to evaluate $Y_c'(\eta)$                                           | 40 |

| 3.2  | Parallel Chebyshev IDCT architecture                                                      | 42 |

| 3.3  | Parallel Chebyshev DCT architecture                                                       | 44 |

| 3.4  | Low-power parallel Chebyshev IDCT architecture with decimation factor                     |    |

|      | of two                                                                                    | 46 |

| 3.5  | Low-power parallel Chebyshev DCT architecture with a decimation factor                    |    |

|      | of two                                                                                    | 47 |

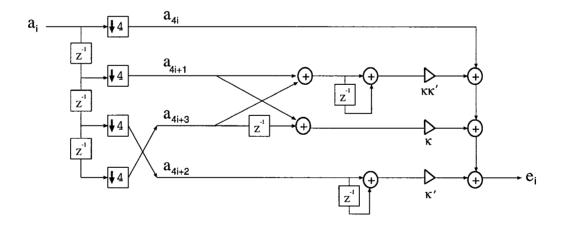

| 3.6  | Evaluation of $e_i$ using a downsampling circuit                                          | 47 |

| 3.7  | Low-power parallel Chebyshev IDCT architecture with a decimation fac-                     |    |

|      | tor of four, where $\eta_n'' = 2(\eta_n')^2 - 1$ and $\kappa_n' = 1/(2\eta_n')$           | 48 |

| 3.8  | Low-power parallel Chebyshev DCT architecture with a decimation factor        |    |

|------|-------------------------------------------------------------------------------|----|

|      | of four, where $\kappa_k''=1/\eta_k''$ and $\eta_k'''=2(\eta_k'')^2-1.$       | 49 |

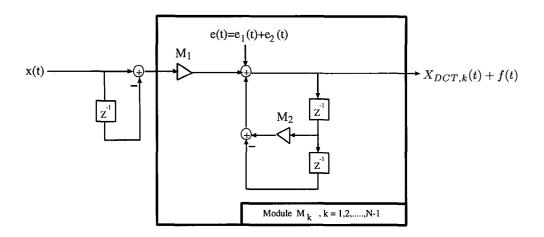

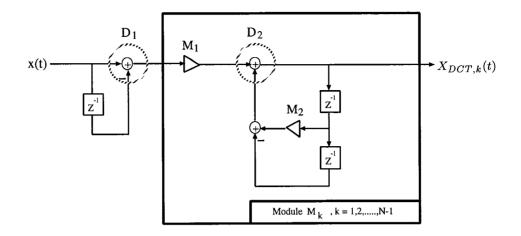

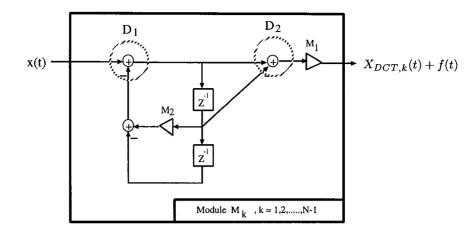

| 3.9  | IIR DCT architecture                                                          | 51 |

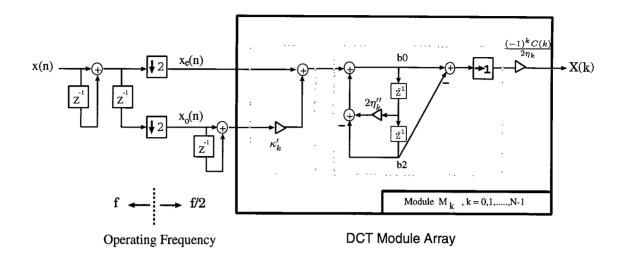

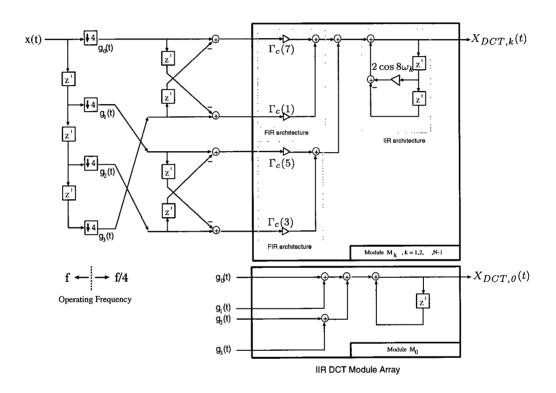

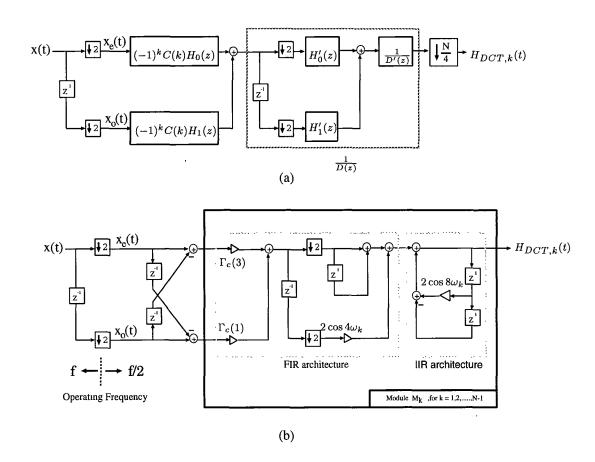

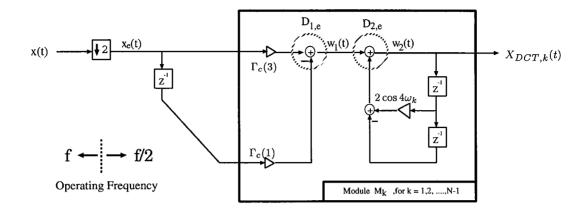

| 3.10 | Low-power polyphase IIR DCT architecture with $M=2.\dots\dots$                | 53 |

| 3.11 | Low-power polyphase IIR DCT architecture with $M=4$                           | 54 |

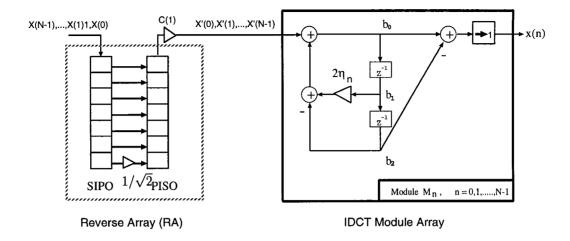

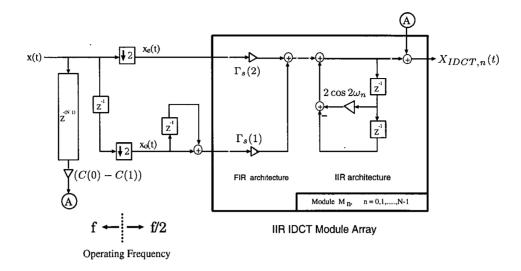

| 3.12 | Low-power polyphase IIR IDCT architecture with $M=2.$                         | 55 |

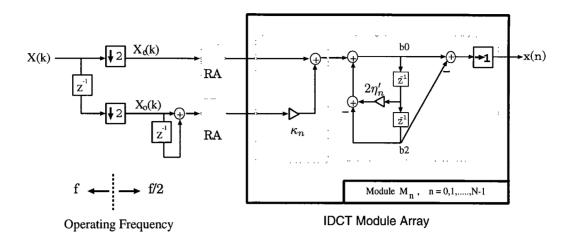

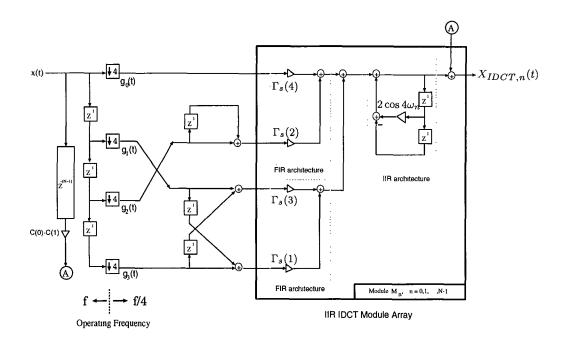

| 3.13 | Low-power polyphase IIR IDCT architecture with $M=4.$                         | 56 |

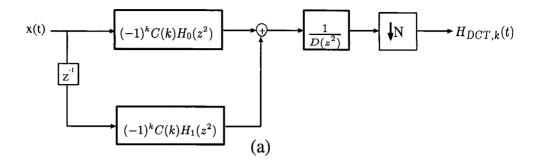

| 3.14 | (a) Polyphase representation of $H_{DCT,k}(z)$ . (b) Polyphase representation |    |

|      | of $H_{DCT,k}(z)$ after applying the noble identity                           | 58 |

| 4.1  | (a) Polyphase representation of $H_{DCT,k}(z)$ in cascade form. (b) Multirate |    |

|      | DCT architecture with logarithmic complexity                                  | 66 |

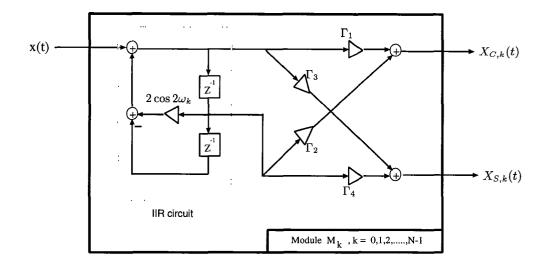

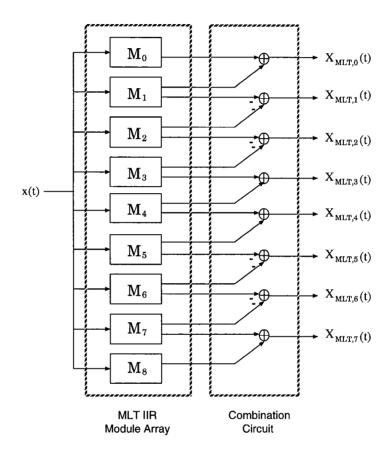

| 4.2  | IIR MLT module design                                                         | 69 |

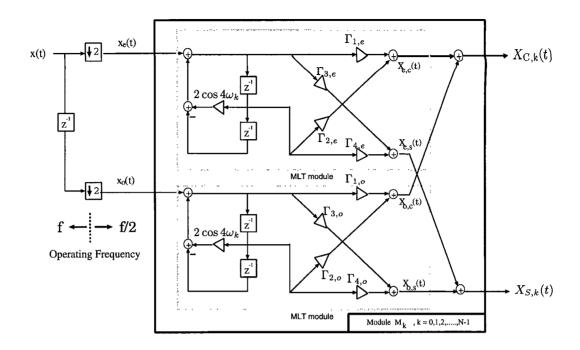

| 4.3  | The time-recursive MLT architecture.                                          | 70 |

| 4.4  | Low-power IIR MLT module design                                               | 71 |

| 5.1  | Rounding error in the IIR DCT architecture                                    | 79 |

| 5.2  | Dynamic range of the IIR DCT architecture                                     | 80 |

| 5.3  | IIR DCT using the direct form II structure                                    | 82 |

| 5.4  | Rounding noise in the low-power IIR DCT architecture with $M=2.$              | 86 |

| 5.5  | Reduced IIR DCT architecture with $M=2.$                                      | 88 |

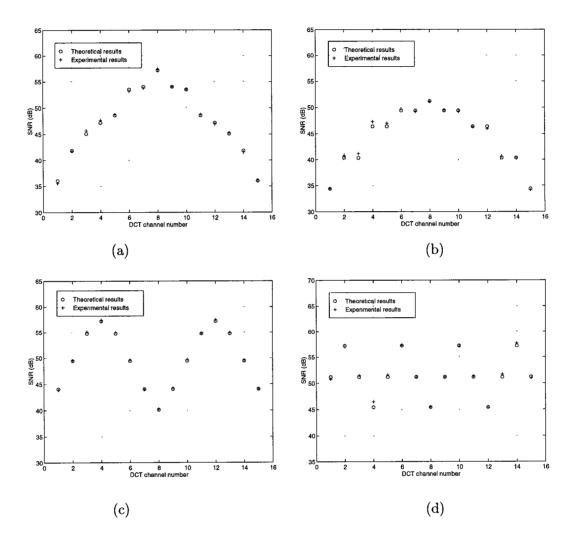

| 5.6  | Average SNR as a function of DCT channel number under fixed-point             |    |

|      | arithmetic ( $N=16,\;B=12$ ). (a) Normal IIR DCT using direct form            |    |

|      | I structure. (b) Normal IIR DCT using direct form II structure. (c)           |    |

|      | Low-power DCT with $M=2$ . (d) Low-power DCT with $M=4$                       | 90 |

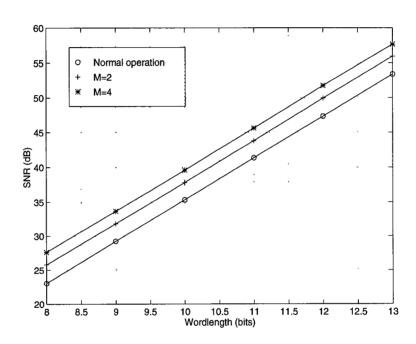

| 5.7  | Average SNR as a function of wordlength under fixed-point arithmetic          |    |

|      | ( $N$ =16). The multirate low-power architectures have better SNR as $M$      |    |

|      | increases.                                                                    | 91 |

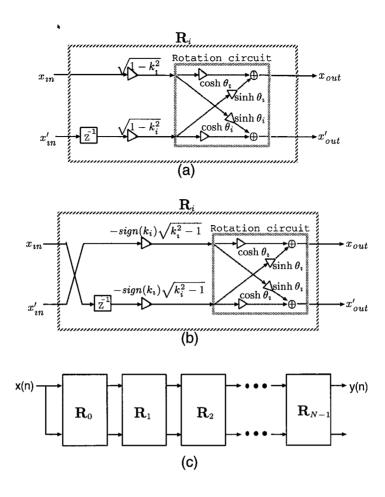

| 6.1  | (a) Basic lattice filter section with $ k_i  < 1$ . (b) Basic lattice filter section |     |

|------|--------------------------------------------------------------------------------------|-----|

|      | with $ k_i  > 1$ . (c) Lattice FIR structure                                         | 95  |

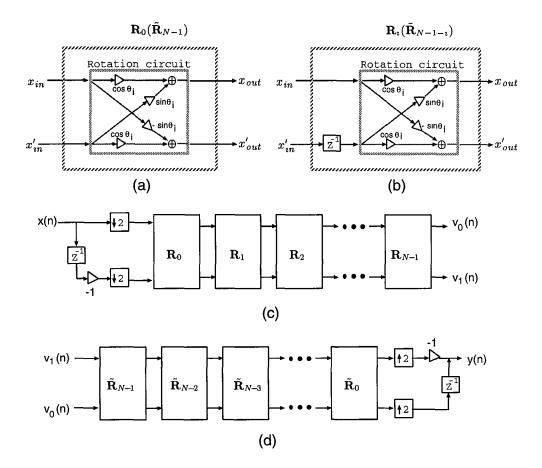

| 6.2  | The two-channel paraunitary QMF lattice: (a),(b) Basic lattice sections.             |     |

|      | (c) The analysis bank. (d) The synthesis bank                                        | 98  |

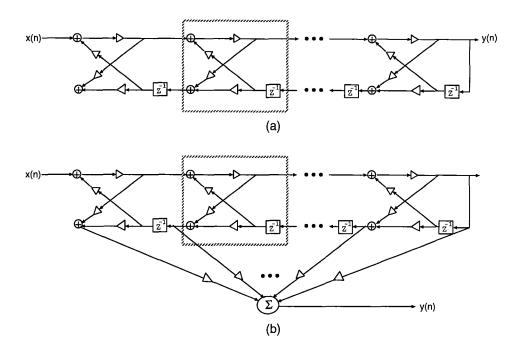

| 6.3  | (a) All-pole IIR lattice. (b) General IIR (ARMA) lattice                             | 100 |

| 6.4  | Second-order IIR lattice architecture                                                | 101 |

| 6.5  | IIR (ARMA) structure based on the second-order IIR lattice module                    | 101 |

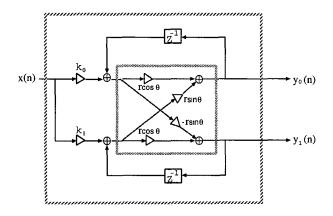

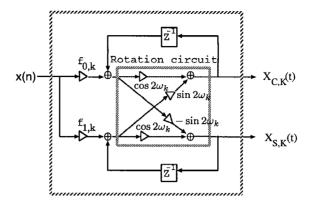

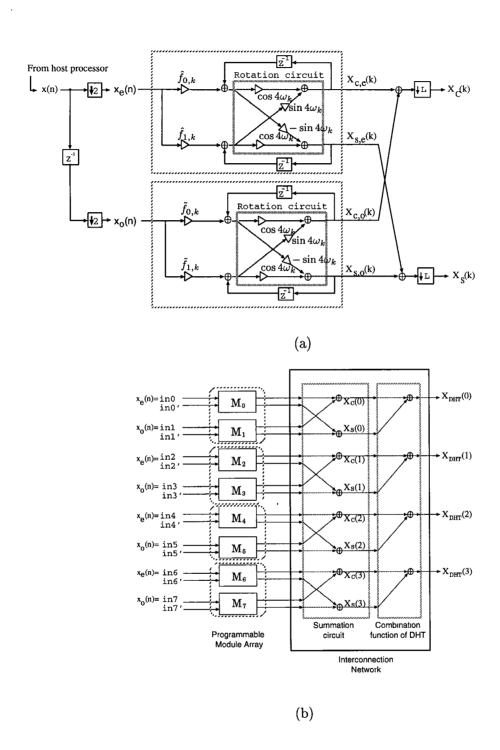

| 6.6  | Rotation-based module for the dual generation of $X_{C,k}(t)$ and $X_{S,k}(t)$       | 104 |

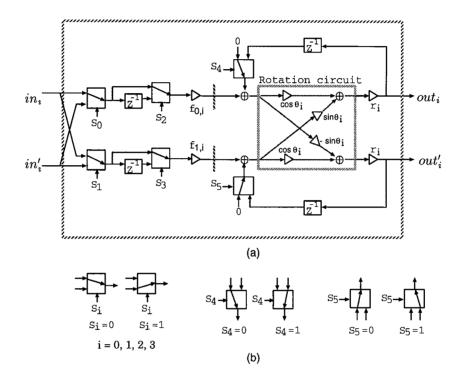

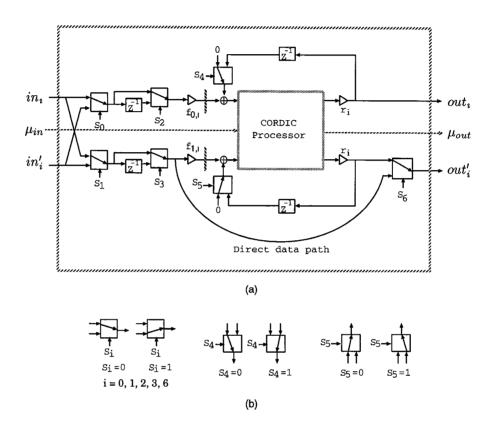

| 6.7  | (a) Programmable module for the FIR/QMF/IIR/DT. (b) Switches used                    |     |

|      | in the module.                                                                       | 105 |

| 6.8  | Overall architecture for FIR filtering                                               | 107 |

| 6.9  | Overall architecture for IIR (ARMA) filtering                                        | 108 |

| 6.10 | (a) Multirate FIR lattice structure. (b) Mapping part (a) to the co-                 |     |

|      | processor architecture.                                                              | 116 |

| 6.11 | (a) Multirate IIR lattice structure. (b) Mapping part (a) to the co-                 |     |

|      | processor architecture                                                               | 118 |

| 6.12 | (a) Multirate architecture for the dual generation of $X_C(k)$ and $X_S(k)$ .        |     |

|      | (b) Multirate 4-point DHT architecture based on 8 programmable modules.              | 121 |

| 6.13 | (a) CORDIC in vector rotation mode. (b) CORDIC in angle accumula-                    |     |

|      | tion mode.                                                                           | 125 |

| 6.14 | (a) QRD-LSL structure. (b) Realizing the QRD-LSL using the CORDIC                    |     |

|      | processor                                                                            | 126 |

| 6.15 | (a) New programmable module with the QRD-LSL feature. (b) Switches                   |     |

|      | used in the module.                                                                  | 127 |

| 6 16 | Realizing the ORD-LSL using the programmable video co-processor                      | 128 |

#### Chapter 1

#### Introduction

Low-power VLSI design has emerged as a major theme in the electronics industry today. One reason is due to the growing markets in portable computing and communication systems. In the past, most research and development efforts focused on increasing the processing speed and reducing the complexity of the chip design. The power consumption of the chip, on the other hand, is given lower priority during the design phase. The scenario has been changed since the advent of personal communications/computing services (PCS). The common feature of the PCS devices is that they demand high-speed data/signal processing, which leads to much higher power consumption than traditional portable applications such as wrist watches and hand-held calculators. Nevertheless, we have only limited power-supply capability of current battery technology. Hence, we are motivated to consider low-power design so as to prolong the operating time of those PCS devices.

The other reason for low-power design arises from the power dissipation problem. As the clock rate and silicon area of IC designs increase, power dissipation of some individual IC components has not only reached the limits of current packaging technology but also affected the reliability/yield in the fabrication process. As an example, the DEC ALPHA 64-bit CPU [1] consumes up to 30 Watts at a clock rate of 200 MHz. The high power dissipation calls for extra cooling systems such as cooling fins and fans, expensive

1

packages, to dissipate the generated heat. As a result, both weight and cost of the system will be increased. This becomes another driving force for the study of low-power VLSI design.

In general, low-power VLSI design can be achieved at all levels of the VLSI system (system, algorithm, architecture, circuit, logic, device, and technology levels). In this dissertation, we focus on developing a new algorithmic/architectural-level low-power design technique based on the **multirate approach**. We apply it to several important digital signal processing (DSP) applications, which leads to new multirate VLSI architectures that can achieve significant power saving compared with the normal design while retaining the same data throughput rate.

The organization of this chapter is as follows. In Section 1.1, current low-power design approaches at different VLSI levels are described. In Section 1.2, we address the motivation of using the multirate approach in lowering the power consumption at the algorithmic/architectural level. In Section 1.3, we give an overview of the results that we obtained by applying this new low-power design technique to the following DSP tasks: general FIR/IIR filtering, transform coding kernel design, and video co-processor design. We conclude with the dissertation organization in Section 1.4.

#### 1.1 Low-Power VLSI Design Approaches

The power dissipation in a well-designed digital CMOS circuit can be modeled as [2]

$$P \approx \alpha \cdot C_{eff} \cdot V_{dd}^2 \cdot f_{clk}, \tag{1.1}$$

where  $\alpha$  is the average fraction of the total node capacitance being switched (also referred to as the activity factor),  $C_{eff}$  is the effective loading capacity,  $V_{dd}$  is the supply voltage, and  $f_{clk}$  is the operating frequency. On the other hand, the delay of the CMOS device

can be approximated as

$$T_D \approx \frac{C_{eff} \times V_{dd}}{I} = \frac{C_{eff} \times V_{dd}}{\mu C_{ox}(W/L)(V_{dd} - V_t)^2},$$

(1.2)

where  $\mu$ ,  $C_{ox}$ , W, L are the device parameters and  $V_t$  is the threshold voltage of the devices. (1.1) and (1.2) play the essential roles in low-power VLSI designs. Namely, in order to lower the total power consumption of the CMOS circuits, we want to reduce the values of  $\alpha$ ,  $V_{dd}$ ,  $C_{eff}$ , and  $f_{clk}$  by applying all possible techniques at all levels of the VLSI system, whereas  $T_D$  is not sacrificed for those parameter changes [3][4][5][6][7]. The existing low-power design approaches are summarized below.

• Device/VLSI technology level: Over the last decade, the CMOS feature size has been reduced from 2  $\mu m$  to 0.35  $\mu m$ . The advance in IC fabrication technology also leads the way to low-power design. Smaller transistor size not only improves the device/circuit speed performance, it also reduces the total silicon area and capacitances, hence the total power consumption. Besides, the increased level of integration allows the designer to use the vacated area for extra circuits to compensate for the device speed reduction due to lower supply voltage (as we will discuss it later). In addition to the reduction of the feature size, lowering the threshold voltage  $V_t$  is another commonly used approach to achieve low-power consumption at the technology level [4][8]. From (1.1), we can see that the delay of the circuit is inversely proportional to  $(V_{dd} - V_t)^2$ . Thus it is desirable to reduce the magnitude of  $V_t$  either to minimize the degradation of speed caused by lowered  $V_{dd}$ , or to allow further reduction in  $V_{dd}$ .

On the other hand, it is predicted that 1.5V (or lower) operation will be needed by the year 2001 for portable product [6]. Since the supply voltage of the conventional scaled CMOS technology will reach its limit at a supply voltage of 1.5 V, an alternate process technology, silicon-on-insulator (SOI), is suggested to replace the CMOS technology [6][9]. The SOI technology allows power supply reduction to 1V

or less and also greatly simplifies the fabrication process. Those merits have made SOI the best candidate for future low-power fabrication technology. In general, the cost of the technology/device approach is most expensive among all low-power techniques since it requires the investment of new semiconductor equipment and technology.

• Circuit approach: There are numerous options available in choosing the basic circuit approach and topology for implementing the given logic and arithmetic functions. As an example, we can employ several design approaches such as carry-ripple, carry-look-ahead, and carry-select to realize the adder circuit [10]. Each approach renders different trade-off in the performance of power/speed/area. At the CMOS circuit level, various circuit design techniques are available; e.g., dynamic versus static CMOS logic, conventional static versus pass-transistor logic, and synchronous versus asynchronous design [3]. As far as power consumption is concerned, the static CMOS logic and asynchronous design are preferable due to their less number of switching activities. The pass-transistor logic family is also a promising candidate since it uses a less number of transistors than the conventional static CMOS circuits for implementing the same logic function [2, Chap.5].

Recently, the low-power digital circuits based on adiabatic-switching technique was introduced [11]. By employing the adiabatic-switching circuits, the signal energies stored on circuit capacitances can be recycled instead of dissipated as heat, which provides a promising power-saving technology at the circuit level.

• Logic-level approach: In CMOS circuits with negligible leakage current, power is dissipated only when there is a transition at the output of the gate (ZERO to ONE or ONE to ZERO in logic value). In the logic-based low-power design, the major focus is to reduce the frequency of energy consuming transitions for given logic functions, *i.e.*, the activity factor  $\alpha$  in (1.1). Existent approaches can be found in

[12][13][14][15]. They basically examine the given logic functions and perform logic optimization/synthesis in such a way that the total number of logic transitions can be minimized for most inputs signals. By doing so,  $\alpha$  can be reduced, hence the total power consumption of the circuits. In general, the power saving of the logic approach is in the range of 20%-75%.

- Architectural/algorithmic approach: From (1.1), we can see that the reduction of the supply voltage is the leveraged way to reduce the total power consumption due to its quadratic dependence. However, the delay will drastically increase as  $V_{dd}$  approaches  $V_t$  (see (1.2)). That is, we suffer from a speed penalty as  $V_{dd}$  goes down. In order to meet the low-power/high-throughput constraint in most DSP applications, the key issue in algorithmic/architectural-level low-power design is to "compensate" the increased delay caused by the lowered supply voltage. Current approaches for compensating the increased delay include the techniques of "parallel processing" and "pipelining" [3][7]. In this dissertation, we propose a new compensation technique based on the multirate approach, which will be discussed in details in the next section.

- System-level approach: The system-level low-power VLSI design evolves from the power-saving techniques which are frequently used in lap-top/notebook computers as well as the energy-saving "green products". When one of the subsystems is idle for a period of time, it may switch to one of the modes—Doze, Nap, Sleep—to save the system power. Recent state-of-the-art CPU designs have employed the same design concept to manage both dynamic and static power of the CPU [16]. The embedded activity management circuit of the CPU provides the capability to shutdown portions of subsystems that are not required in current or impending operations. Therefore, significant power saving can be achieved. There are two design issues involved in the system-level low-power design. One is the partitioning of the

system into submodules that have high interconnection density within themselves. By doing so, the influence of shutting down one submodule to other submodules can be minimized. For ASIC designs that use multichip modules (MCMs) implementation, the partitioning can be done by employing the systematic approach discussed in [17]. The other is the design of additional hardware/software for monitoring the working status of each submodule of the chip, which will introduce extra cost and weight to the system.

Among these low-power techniques, the algorithmic/architectural approach is the most promising one [7]. Firstly, the algorithmic/architectural low-power design is achieved by reformulating the algorithms and mapping them to efficient low-power VLSI architectures to compensate the speed penalty caused by low supply voltage. Basically, we only trade more chip area for low power consumption under current technology, without invoking dedicated circuit design, new expensive device materials, and advanced VLSI fabrication technology. Compared with other approaches, the algorithmic/architectural low-power design is one of the most economical ways to save power. Secondly, the power saving of the the algorithmic/architectural approach is in the range of 70%-90% <sup>1</sup> (as we will show it in this dissertation). Therefore, the algorithmic/architectural-level approach provides the most leveraged way to achieve low-power consumption when both effectiveness and cost are taken into consideration.

# 1.2 Algorithmic/Architectural-level Low-Power Design Using the Multirate Approach

The architectural-level low-power design was first proposed by Chandrakasan *et al.* [3]. In [3], the techniques of "parallel processing" and "pipelining" were suggested to com-

<sup>&</sup>lt;sup>1</sup>The current goal is to reduce the total power dissipation of the electronics systems to two orders of magnitude less than what would have been with the conventional technology [6].

pensate the speed penalty, and a simple comparator circuit was used to demonstrate how parallel independent processing of the data can achieve good compensation at the architectural level. However, in most DSP applications, the problems encountered are much more complex. It is almost impossible to directly decompose the problems into independent and parallel tasks. Therefore, the properties of the DSP algorithms should be fully exploited in order to develop efficient techniques to compensate the loss of performance under low-power operations. The main issue here is to reformulate the algorithms so that the desired output can be obtained without hindering the system performance such as data throughput rate. We call such an approach the algorithm-based low-power design.

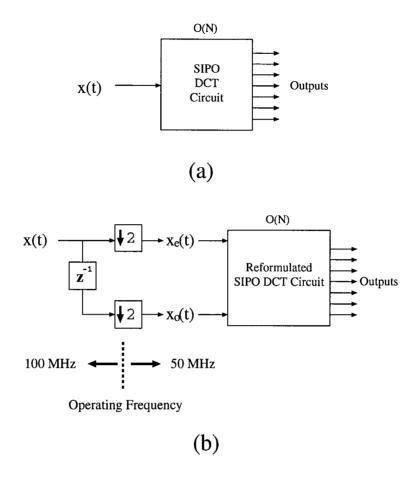

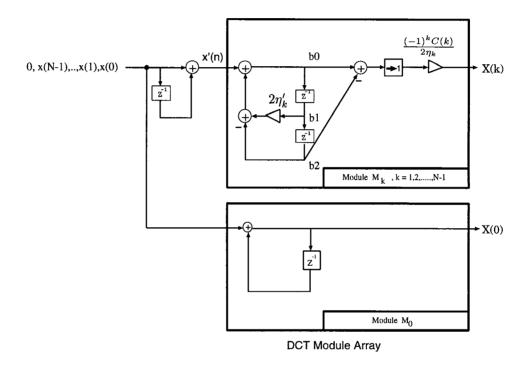

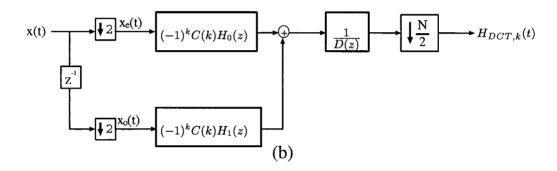

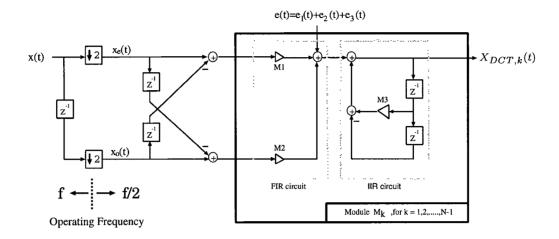

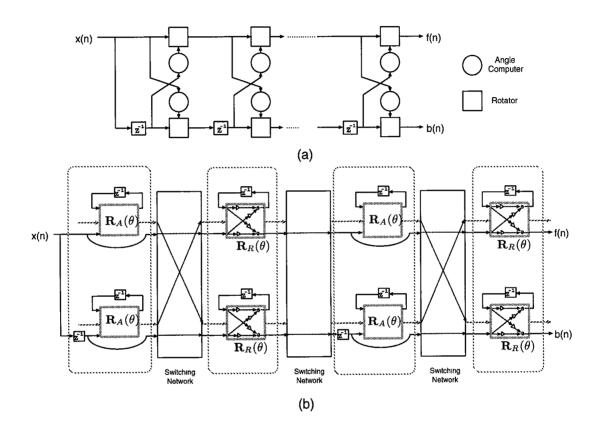

In this dissertation, we propose a new technique—the multirate approach—to compensate the aforementioned speed penalty. To motivate the idea, let us consider the discrete cosine transform (DCT) architecture in Fig. 1.1. For most of the existing serial-input-parallel-output (SIPO) DCT architectures [18][19], the processing rate of the operators must be as fast as the input data rate (see Fig. 1.1(a)). In our low-power design, the DCT is computed from the reformulated circuit using the decimated sequences (Fig. 1.1(b)). It is now a multirate system that operates at two different sample rates. Since the operating speed of the processing elements is reduced to half of the original data rate while the data throughput rate is still maintained, the speed penalty is compensated at the architectural level. Suppose that the  $C_{eff}$  is approximately doubled due to the hardware overhead in the reformulated circuit. Since all the operations are at half of the original speed, the lowest possible voltage can be reduced from 5 V to 2.9 V [3]. Using the CMOS power dissipation model of (1.1), the overall power consumption of the multirate design can be estimated as

$$(2C_{eff})(\frac{2.9V}{5V})^2(\frac{1}{2}f) \approx 0.34P_0, \tag{1.3}$$

where  $P_0$  denotes the power consumption of the original system. Therefore, the multirate approach provides a direct and efficient way for the low-power design at the algorith-

Figure 1.1: (a) Original SIPO DCT circuit. (b) Low-power DCT circuit using the multirate approach.

mic/architectural level.

#### 1.3 Main Contributions

Based on the proposed new algorithmic/architectural-level low-power design technique, several significant results are developed in this dissertation and are summarized as follows:

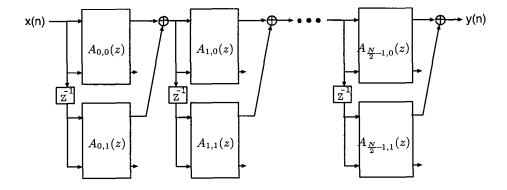

- 1. Design methodology for multirate FIR/IIR filtering architectures: We present a design methodology for the low-power design of any given FIR/IIR DSP systems. The users can simply follow the design steps to convert a speed-demanding system function into its equivalent multirate transfer function. Since the data rate in the resulting multirate filtering architecture is M-times slower (where M is a positive integer) than the original data rate while maintaining the same throughput rate, we can apply this feature to either the low-power implementation, or the speed-up of the DSP systems. The proposed design methodology provides VLSI designers a systematic tool to design low-power DSP systems at the algorithmic/architectural level. Furthermore, it can be incorporated into the design of high-level synthesis computer-aided-design (CAD) tools for power minimization.

- 2. Low-power transform coding architecture design: We demonstrate how the multirate approach can be applied to low-power but high-speed transform coding architectures. We start with the derivations of the multirate DCT/IDCT architectures. The resulting multirate low-power architectures are regular, modular, and free of global communications. Also, the compensation capability is achieved at the expense of locally increased hardware and data paths. As a consequence, they are very suitable for VLSI implementation. We also consider the design of low-power architectures that can lower the power consumption with only O(log M) increase in hardware complexity. The multirate DCT/IDCT design is extended to a unified low-power transform coding architecture that can perform most of the existing discrete sinusoidal transforms based on the same processing elements. Moreover, we perform the finite-precision analysis of the DCT architectures under the normal and multirate operations. Using the analytical results, we can choose the optimal wordlength for each DCT channel under the predetermined signal-to-noise ratio (SNR) constraint. Hence, the total number of switching events and the silicon

area are further reduced, and so is the power consumption of the DCT chip. These design issues constitute a framework of the algorithm-based low-power design with an application to transform coding kernel design.